簡介

處理器間中斷就是一個 CPU 向系統中的目標 CPU傳送中斷信號,以使目標CPU執行特定的操作。CPU將處理器間中斷(IPI) 作為信號直接放在 APIC 匯流排上傳輸,並不通過 IRQ 中斷線。Linux 在核心中使用了三種處理器間中斷。CALL_FUNCTION _VECTOR:該中斷被發往所有的 CPU,但不包括傳送者。該中斷促使目標 CPU 執行特定的操作,實際上就是運行一個隨參數傳遞過來的函式。

機制

OS/360的M65MP選件使用S/360的直接控制功能生成另一個處理器上的中斷;在S/370及其後繼者,包括z/Architecture上,SIGNAL PROCESSOR指令提供了一個更正式的接口。在使用高級可程式中斷控制器(APIC)的IBM PC兼容機上,常藉助APIC發出IPI信號。當CPU希望向另一個CPU傳送中斷時,它會將中斷向量和目標的本地APIC標識符存儲在自己的本地APIC中斷命令暫存器(ICR)中。訊息隨後經由APIC匯流排傳送到目標的本地APIC,它因此發出一個相應的中斷至它自己的CPU。例如在運行Microsoft Windows的多處理器系統中,除了上面列出的,處理器還可以出於下列原因中斷另一個處理器:排隊輪候DISPATCH_LEVEL中斷,以調度執行特定執行緒;核心調試器斷點。

中斷控制器

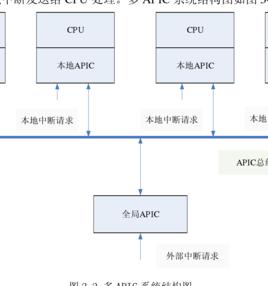

傳統的 X86 處理器使用 8259A 中斷控制器。它接收多個外部中斷源並傳送給系統中單一 CPU 進行處理。如果在多核的 SMP 結構中採用 8259A 中斷控制器,那么中斷分發的做法就是先將所有外部中斷分為若干組,每一組中斷被傳送到一個 8259A 中斷控制器上,然後 8259A 再與某一 CPU 進行連線,也就是 8259A 再將中斷髮送給這個 CPU。這種不能動態分配中斷請求的做法使得硬體的設計變得非常複雜,而且難以擴展。因此,Intel 設計出一種更加通用的中斷控制器,稱為高級可程式中斷控制器 APIC(Advanced Programable Interrupt Contrallor)。首先,在SMP 結構中,有一個接收所有外部中斷、全局的 APIC,被稱為 I/O APIC,另一方面,由於 CPU 之間需要進行核間通信,也就是處理器間相互傳送中斷請求,所以每個 CPU 都有一個本地 APIC。本地 APIC 負責收集本地中斷請求和外部傳送過來的中斷,再將該中斷髮送給 CPU處理。

集成在 CPU 晶片內部的本地 APIC 與外部的 I/O APIC 相互配合使用,既可以用於 SMP 結構,也可以用於單 CPU 結構。本地 APIC 中包含一個產生時鐘中斷的定時器,所以極端情況下還可以選擇只使用本地 APIC,而不需要 I/O APIC 的配合,可見這是一個高可配的系統。即使使用了APIC,每個 CPU 仍然可以單獨連線到8259A 中斷控制器上。I/O APIC 由四個部分組成:一組 24 條 IRQ 線、一張 24 項的中斷重定向表、可程式暫存器以及傳送和接收 APIC 信息的一個信息單元。APIC 的中斷優先權並不與引腳號相關聯,而是通過中斷重定向表的表項單獨編程加以指明,該表項還可以指明中斷的目標 CPU。中斷重定向表用於把每個外部 IRQ 中斷請求信號轉換為一條訊息,然後通過 APIC 匯流排把訊息傳送給一個或多個目標 CPU 的本地 APIC單元 。

分發方式

系統分發 IRQ 中斷給 CPU 主要有兩種方式:靜態分發和動態分發。

靜態分發:所有本地 APIC 都會被靜態寫入中斷重定向表的表項中,IRQ 中斷請求信號會傳送給這些表項的列出的本地 APIC。然後本地 APIC 再將中斷髮送給目標 CPU。

動態分發:在所有 CPU 正在執行的進程中,如果某個 CPU 正在執行的進程的優先權最低,IRQ 中斷請求信號就傳遞給這個 CPU,這就是所謂的最低優先權模式。每個本地 APIC 內部都包含一個可程式任務優先權暫存器 TPR,該暫存器計算運行進程的優先權,以供中斷分發參考使用。作業系統核心在進程切換時都會對這個暫存器進行修改。如果多個 CPU 有相同的最低優先權,這種情況是可能的,此時系統就利用仲裁技術來分配 CPU 的負荷。在本地APIC 中有一個仲裁優先權暫存器中,初始化時會為每個 CPU 都分配一個 0—l5 範圍內的值。當某 CPU接收到一個中斷時,其仲裁優先權的值就自動設定為 0,而其他 CPU 的仲裁優先權都增加一。當仲裁優先權暫存器的值大於15 時,就將獲取中斷的那個 CPU 的前一個仲裁優先權加 l,作為當前 CPU 的仲裁優先權。因此,中斷在 CPU 之間以輪轉方式進行分發,並且各個 CPU 任務優先權相同。多 APIC 系統還處理 CPU 之間產生的處理器間中斷。某 CPU 為了要向目標CPU 傳送中斷,它先要將中斷向量和目標 CPU 的本地 APIC 的 ID 存入中斷指令暫存器 ICR 中,然後經過 APIC 匯流排向目標 CPU 傳送核間中斷,目標CPU 接收中斷,然後進行中斷處理。處理器間中斷(IPI)是 SMP 體系結構非常重要的組成部分,利用它可以進行 CPU 間的通信,有效地提升系統的效率。