基本信息

計算機科學中,中斷(Interrupt)是指處理器接收到來自硬體或軟體的信號,提示發生了某個事件,應該被注意,這種情況就稱為中斷。通常,在接收到來自外圍硬體(相對於中央處理器和記憶體)的異步信號,或來自軟體的同步信號之後,處理器將會進行相應的硬體/軟體處理。發出這樣的信號稱為進行中斷請求(interrupt request,IRQ)。硬體中斷導致處理器通過一個運行信息切換(context switch)來保存執行狀態(以程式計數器和程式狀態字等暫存器信息為主);軟體中斷則通常作為CPU指令集中的一個指令,以可程式的方式直接指示這種運行信息切換,並將處理導向一段中斷處理代碼。中斷在計算機多任務處理,尤其是即時系統中尤為有用。這樣的系統,包括運行於其上的作業系統,也被稱為“中斷驅動的”(interrupt-driven)。

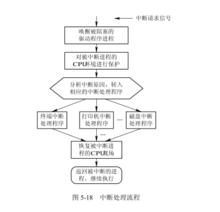

執行中斷即處理機回響中斷並處理中斷,計算機執行中斷一般是通過調用中斷處理程式來完成的。中斷處理程式:用於保存被中斷進程的 CPU 環境,轉入相應的中斷處理程式進行處理,處理完後再恢復被中斷進程的現場後返回到被中斷進程。

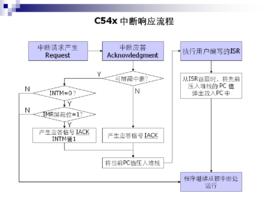

執行中斷步驟

中斷處理層的主要工作有:進行進程上下文的切換,對處理中斷信號源進行測試,讀取設備狀態和修改進程狀態等。由於中斷處理與硬體緊密相關,對用戶及用戶程式而言,應該儘量加以禁止,故應該放在作業系統的底層進行中斷處理,系統的其餘部分儘可能少地與之發生聯繫。當一個進程請求 I/O 操作時,該進程將被掛起,直到 I/O 設備完成 I/O 操作後,設備控制器便向 CPU 傳送一中斷請求,CPU 回響後便轉向中斷處理程式,中斷處理程式執行相應的處理,處理完後解除相應進程的阻塞狀態。對於為每一類設備設定一個I/O進程的設備處理方式,其中斷處理程式的處理過程分成以下幾個步驟。

喚醒被阻塞的驅動(程式)進程

當中斷處理程式開始執行時,首先去喚醒處於阻塞狀態的驅動(程式)進程。如果是採用了信號量機制,則可通過執行 signal 操作,將處於阻塞狀態的驅動(程式)進程喚醒;在採用信號機制時,將傳送一信號給阻塞進程。

保護被中斷進程的 CPU 環境

執行中斷

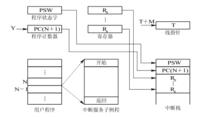

執行中斷通常由硬體自動將處理機狀態字 PSW 和程式計數器(PC)中的內容,保存在中斷保留區(棧)中,然後把被中斷進程的 CPU 現場信息(即包括所有的 CPU 暫存器,如通用暫存器、段暫存器等內容)都壓入中斷棧中,因為在中斷處理時可能會用到這些暫存器。圖 給出了一個簡單的保護中斷現場的示意圖。該程式是指令在 N 位置時被中斷的,程式計數器中的內容為 N+1,所有暫存器的內容都被保留在棧中。

轉入相應的設備處理程式

由處理機對各箇中斷源進行測試, 以確定引起本次中斷的 I/O 設備, 並傳送一應答信號給發出中斷請求的進程,使之消除該中斷請求信號,然後將相應的設備中斷處理程式的入口地址裝入到程式計數器中,使處理機轉向中斷處理程式。

中斷處理

對於不同的設備,有不同的中斷處理程式。該程式首先從設備控制器中讀出設備狀態,以判別本次中斷是正常完成中斷,還是異常結束中斷。若是前者,中斷程式便進行結束處理;若還有命令,可再向控制器傳送新的命令,進行新一輪的數據傳送。若是異常結束中斷,則根據發生異常的原因做相應的處理。

恢復被中斷進程的現場

執行中斷

執行中斷當中斷處理完成以後,便可將保存在中斷棧中的被中斷進程的現場信息取出,並裝入到相應的暫存器中, 其中包括該程式下一次要執行的指令的地址 N+1、 處理機狀態字 PSW,以及各通用暫存器和段暫存器的內容。這樣,當處理機再執行本程式時,便從 N+1 處開始,最終返回到被中斷的程式。

I/O 操作完成後,驅動程式必須檢查本次 I/O 操作中是否發生了錯誤,並向上層軟體報告,最終向調用者報告本次 I/O 的執行情況。除了上述的第 4 步外,其它各步驟對所有 I/O設備都是相同的,因而對於某種作業系統,例如 UNIX 系統,是把這些共同的部分集中起來,形成中斷總控程式。每當要進行中斷處理時,都要首先進入中斷總控程式。而對於第 4 步,則對不同設備須採用不同的設備中斷處理程式繼續執行。圖示出了中斷處理流程。

中斷分類

硬體中斷(Hardware Interrupt)

可禁止中斷(maskable interrupt)。硬體中斷的一類,可通過在中斷禁止暫存器中設定位掩碼來關閉。

非可禁止中斷(non-maskable interrupt,NMI)。硬體中斷的一類,無法通過在中斷禁止暫存器中設定位掩碼來關閉。典型例子是時鐘中斷(一個硬體時鐘以恆定頻率—如50Hz—發出的中斷)。

處理器間中斷(interprocessor interrupt)。一種特殊的硬體中斷。由處理器發出,被其它處理器接收。僅見於多處理器系統,以便於處理器間通信或同步。

偽中斷(spurious interrupt)。一類不希望被產生的硬體中斷。發生的原因有很多種,如中斷線路上電氣信號異常,或是中斷請求設備本身有問題。

軟體中斷(Software Interrupt)

軟體中斷。是一條CPU指令,用以自陷一個中斷。由於軟中斷指令通常要運行一個切換CPU至核心態(Kernel Mode/Ring 0)的子例程,它常被用作實現系統調用(System call)。

處理器通常含有一個內部中斷禁止位,並允許通過軟體來設定。一旦被設定,所有外部中斷都將被系統忽略。這個禁止位的訪問速度顯然快於中斷控制器上的中斷禁止暫存器,因此可提供更快速地中斷禁止控制。

如果一個中斷使得機器處於一種確定狀態,則稱為精確中斷(precise interrupt)。精確中斷須保證:

程式計數器的值被保存在已知位置。

程式計數器所指向的指令之前的所有指令已被執行完畢。

程式計數器所指向的指令之後的所有指令不可被執行。如果中斷信號到來後而轉入處理前發生了任何針對暫存器/記憶體的更改,都必須予以還原。

程式計數器所指向的指令地執行狀態已知。

倘無法滿足以上條件,此中斷被稱作非精確中斷(imprecise interrupt)。

中斷儘管可以提高計算機處理性能,但過於密集的中斷請求/回響反而會影響系統性能。這類情形被稱作中斷風暴(interrupt storm)。