PN結隔離

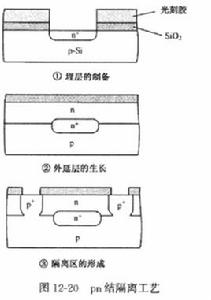

pn結隔離是積體電路生產中比較常用的方法,特別是在一些無特殊要求的小規模積體電路中。它是利用pn結反向偏置時呈高電阻性,來達到各元件互相絕緣隔離的目的。實現隔離有多種方法,但用得最多的還是一次外延、二次擴散pn結隔離工藝,簡稱標準pn結隔離或pn結隔離 。

為了實現pn結隔離,襯底材料必須選用p型單晶,以便和n型外延層之間形成pn結。這一pn結擊穿電壓的大小主要取決於襯底電阻率的高低。從提高擊穿電壓和減小隔離結寄生電容考慮,襯底的電阻率高一點好。但選得過高,在長時間的隔離擴散中,會增加外延層向襯底的推移,使隔離時間加長。同時高阻的單晶較貴,因此電阻率不能取得太高,在一般電路中為8到13歐姆厘米。為了得到平坦均勻的擴散結面,還應選用 晶向的矽單晶。厚度一般為300到350微米,應選用位錯密度較低(一般應小於3000個/平方厘米),有害雜質少的矽單晶片 。

器件隔離

器件隔離圖1 PN結隔離工藝

LOCOS隔離

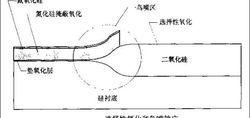

傳統的矽局部氧化(Local Oxidation of Sillicon, LOCOS)隔離技術是利用光刻刻蝕技術在矽基板上的氮化矽上開出氧化視窗,利用氮化矽的掩模作用在大約1000攝氏度的高溫下對沒有氮化矽覆蓋的場區進行氧化。氧化後氧化層表面將高出矽基板表面,高度大約是氧化膜厚度的55%,形成一定程度的不平坦表面,給後續工藝帶來不利影響。再者,氧化生長時,橫向的氧化生長將向器件的有源區延伸,形成所謂的“鳥嘴”現象。“鳥嘴”的出現,不但占據了一定的有源區面積,而且在極小尺寸下,使得漏電流問題越來越突出,極大地影響到器件的性能 。

器件隔離

器件隔離圖2 LOCOS隔離的鳥嘴效應

溝槽隔離

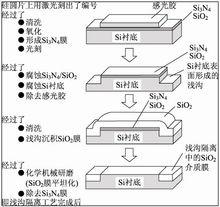

溝槽(Shallow Trench Isolation, STI)隔離技術起源於80年代,由於它的高成本和工藝的不成熟性,直到最近一兩年才被人們所接受。該工藝是一種完全平坦的、完全無“鳥嘴”現象的新型隔離技術。其工藝流程如圖所示,隔離技術完全迴避了高溫工藝;嚴格保證器件有源區的面積;矽基板表面與隔離介質表面完全在同一平面上;改善了最小隔離間隔和結電容。同時,低溫工藝也可以潛在地增加產量,降低成本。這些優點使得STI隔離成為深亞微米時代器件不可或缺的隔離技術。STI隔離主要適應極小尺 寸器件對極小特徵尺寸、器件可靠性的要求。在 極小尺寸下,要求場區和有源區的面積非常小; 同時,對器件的漏電流也極為敏感。STI隔離工藝 主要有以下各關鍵工藝:氧化和氮化矽生長、溝壑光刻刻蝕、HDP High Density Plasma,高密度電漿)二氧化矽生長、二氧化矽CMP Chemical Mechanical Planarization)、氮化矽去除 等工藝步驟 。

器件隔離

器件隔離圖3 溝槽隔離工藝步驟