簡介

特定處理任務

例如,數學協處理器可以控制數字處理;圖形協處理器可以處理視頻繪製。例如,intel pentium 微處理器就包括內置的數學協處理器。

核心相連

協處理器可以附屬於ARM處理器。一個協處理器通過擴展指令集或提供配置暫存器來擴展核心處理功能。一個或多個協處理器可以通過協處理器接口與ARM核心相連 。

協處理器可以通過一組專門的、提供load-store類型接口的ARM指令來訪問。例如協處理器15(CP15),ARM處理器使用協處理器15的暫存器來控制cache、TCM和存儲器管理。

擴展指令集

協處理器也能通過提供一組專門的新指令來擴展指令集。例如,有一組專門的指令可以添加到標準ARM指令集中,以處理向量浮點(VFP)運算。

這些新指令是在ARM流水線的解碼階段被處理的。如果在解碼階段發現是一條協處理器指令,則把它送給相應的協處理器。如果該協處理器不存在,或不認識這條指令,則ARM認為發生了未定義指令異常。這也使得編程者可以用軟體來仿真協處理器的行為(使用未定義指令異常服務子程式)。

內部結構

協處理器

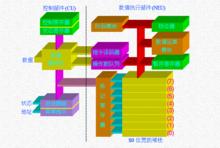

協處理器協處理器80x87的內部結構如圖所示。它可分為二個主要部分:控制部件(CU)和數值執行部件(NEU)。

控制部件(CU)把協處理器接到CPU的系統匯流排上,協處理器和CPU都監視正在執行的指令流。如果當前將要執行的指令是協處理器指令(即:ESCape指令),那么,協處理器會自動執行它,否則,該指令將交給CPU來執行。

數值執行部件(NEU)複製執行所有的協處理器指令,它有一個用8個80位的暫存器組成的堆疊,該堆疊用於以擴展精度的浮點數據格式來存放數學指令的運算元和運算結果。在協處理器指令的執行過程中,要么指定該堆疊暫存器中的數據,要么使用壓棧/出棧機制來從棧頂存放或讀取數據。

在NEU部件中,還有一些記錄協處理器工作狀態的暫存器,如:狀態暫存器、控制暫存器、標記暫存器和異常指針暫存器等。有關這些暫存器的作用將在後面給予分別介紹。

現代PC協處理器

2006年,AGEIA宣布了PhysX物理加速卡, PhysX被設計來處理那些耗時複雜的物理計算。2008年,Nvidia收購了AGEIA,NVIDIA將PhysX物理引擎,利用CUDA技術,由顯示核心加速運算。

2008年,Khronos Group發布OpenCL,這是一個通用語言,支持ATI/AMD和Nvidia的GPU。

2012年,Intel宣布Intel Xeon Phi協處理器。

2013年,蘋果在iPhone 5s上首次推出了M7運動協處理器 。

超級CPU

協處理器的消亡

80486CPU之前有協處理器,提高浮點運算能力,那時cpu較弱才有的協處理器,速度是原來數百倍不止,pc機一般不存在協處理器了。

ARM 微處理器

ARM 微處理器可支持多達 16 個協處理器,用於各種協處理操作,在程式執行的過程中,每個協處理器只執行針對自身的協處理指令,忽略 ARM 處理器和其他協處理器的指令。ARM 的協處理器指令主要用於 ARM 處理器初始化 ARM 協處理器的數據處理操作,以及在ARM 處理器的暫存器和協處理器的暫存器之間傳送數據,和在 ARM 協處理器的暫存器和存儲器之間傳送數據。 ARM 協處理器指令包括以下 5 條: — CDP 協處理器數操作指令— LDC 協處理器數據載入指令— STC 協處理器數據存儲指令— MCR ARM 處理器暫存器到協處理器暫存器的數據傳送指令— MRC 協處理器暫存器到ARM 處理器暫存器的數據傳送指令。

ARM:協處理器包括以下5條:

CDP:協處理器數據操作指令。

LDC:協處理器數據載入指令。

STC:協處理器數據存儲指令。

MCR:ARM處理器暫存器到協處理器暫存器的數據傳送指令。

MRC:協處理器暫存器到ARM處理器暫存器的數據傳送指令 。