PCI匯流排

PCI

PCI普通PCI匯流排頻寬一般為132MB/s(在32bit/33Mhz下)或者264MB/s(在32bit/66Mhz下)。對於普通的音效卡、百兆網卡、Modem卡等擴展設備一般使用的是132MB/s的傳輸速率,這種設備的金手指特徵一般是與PCI插槽對應(長-短),而對於部分PCI顯示卡、千兆網卡、磁碟陣列卡、USB2.0或者火線卡等需要較高頻寬的PCI設備一般可以使用264MB/s的頻寬,這種設備的特徵是金手指一般是三段式(短-長-短)。至於設備是否工作在66Mhz下可以通過軟體everest查看,在PCI設備欄中選中需要觀察設備並查看“66Mhz操作”是否為“已支持”,如果顯示為“不支持”則表示這個設備最多只能使用133MB/s的頻寬。Intel在2001年春季的IDF上,正式公布了旨在取代PCI匯流排的第三代I/O技術,該規範由Intel支持的AWG(Arapahoe Working Group)負責制定。2002年4月17日,AWG正式宣布3GIO1.0規範草稿制定完畢,並移交PCI-SIG(PCI特別興趣小組,PCI-Special Interest Group)進行審核。開始的時候大家都以為它會被命名為Serial PCI(受到串列ATA的影響),但最後卻被正式命名為PCI Express,Express意思是高速、特別快的意思。

PCI

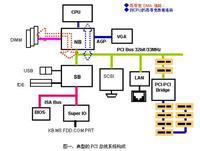

PCIPCI匯流排是一種不依附於某個具體處理器的局部匯流排。從結構上看,PCI是在CPU和原來的系統匯流排之間插入的一級匯流排,具體由一個橋接電路實現對這一層的管理,並實現上下之間的接口以協調數據的傳送。管理器提供了信號緩衝,使之能支持10種外設,並能在高時鐘頻率下保持高性能。PCI匯流排也支持匯流排主控技術,允許智慧型設備在需要時取得匯流排控制權,以加速數據傳送。

PCI匯流排的地址匯流排與數據匯流排是分時復用的,支持即插即用 (plug and play)、中斷共享等功能。分時復用的好處是一方面可以節省接外掛程式的引腳數,另一方面便於實現突發數據傳輸。

數據傳輸時,由一個PCI設備做發起者(主控、Initiator或Master),而另一個PCI設備做目標(從設備、Target或Slave)。匯流排上所有時序的產生與控制都有Master來發起。PCI匯流排在同一時刻只能供一堆設備完成傳輸。這就要求有一個仲裁機構來決定誰有權拿到匯流排的主控權。

特點

即插即用:是指當板卡插入系統時,系統會自動對板卡所需資源進行分配,如基地址、中斷號等,並自動尋找相應的驅動程式。而不象舊的ISA板卡,需要進行複雜的手動配置。

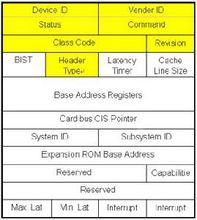

實際的實現遠比說起來要複雜。在PCI板卡中,有一組暫存器,叫"配置空間"(Configuration Space),用來存放基地址與記憶體地址,以及中斷等信息。

以記憶體地址為例。當上電時,板卡從ROM里讀取固定的值放到暫存器中,對應記憶體的地方放置的是需要分配的記憶體位元組數等信息。作業系統要跟據這個信息分配記憶體,並在分配成功後把相應的暫存器中填入記憶體的起始地址。這樣就不必手工設定開關來分配記憶體或基地址了。對於中斷的分配也與此類似。

中斷共享:ISA卡的一個重要局限在於中斷是獨占的,而我們知道計算機的中斷號只有16個,系統又用掉了一些,這樣當有多塊ISA卡要用中斷時就會有問題了。

PCI

PCIPCI匯流排的中斷共享由硬體與軟體兩部分組成。硬體上,採用電平觸發的辦法:中斷信號在系統一側用電阻接高,而要產生中斷的板卡上利用三極體的集電極將信號拉低。這樣不管有幾塊板產生中斷,中斷信號都是低;而只有當所有板卡的中斷都得到處理後,中斷信號才會回復高電平。

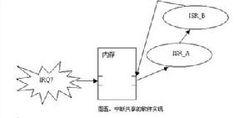

軟體上,採用中斷鏈的方法:假設系統啟動時,發現板卡A用了中斷7,就會將中斷7對應的記憶體區指向A卡對應的中斷服務程式入口ISR_A;然後系統發現板卡B也用中斷7,這時就會將中斷7對應的記憶體區指向ISR_B,同時將ISR_B的結束指向ISR_A。以此類推,就會形成一個中斷鏈。而當有中斷髮生時,系統跳轉到中斷7對應的記憶體,也就是ISR_B。ISR_B就要檢查是不是B卡的中斷,如果是,要處理,並將板卡上的拉低電路放開;如果不是,則呼叫ISR_A。這樣就完成了中斷的共享。

優缺點

PCI

PCI優點: 匯流排結構簡單、成本低、設計簡單。缺點也比較明顯, 並行匯流排無法連線太多設備,匯流排擴展性比較差,線間干擾將導致系統無法正常工作;2) 當連線多個設備時,匯流排有效頻寬將大幅降低,傳輸速率變慢;為了降低成本和儘可能減少相互間的干擾,需要減少匯流排頻寬,或者地址匯流排和數據匯流排採用復用方式設計,這樣降低了頻寬利用率。 PCI Express匯流排是為將來的計算機和通訊平台定義的一種高性能,通用I/O互連匯流排。

版本

2002年7月23日,PCI-SIG 正式公布了PCI Express 1.0規範,並於2007年初推出2.0規範(Spec 2.0),將傳輸率由PCI Express 1.1的2.5GB/s提升到5GB/s;目前主流的顯示卡接口都支持PCI-E 2.0。PCI-X2.0標準傳輸速率最大4.3GB/s。

PCI2.2允許66MHz的信號傳輸(需要在3.3伏特的信號,傳輸速率峰值為533MB每秒)。

PCI2.3允許使用3.3伏特和通用標識符,但在5伏特的情況下不能使用。

PCI3.0是PCI匯流排的最後一個官方版本,徹底取消了對使用5伏特的設備的支持。

PCI-X稍稍改變了協定並增加了資料傳輸速率到133MHz(傳輸速率峰值為1066MB/s)。

PCI-X2.0指定了266MHz(傳輸速率峰值為2133MB/s)和533MHz速率,擴充可規劃空間至4096bytes,增加了16-bit的可變匯流排並且允許1.5伏特的電壓訊號。

PCI

PCI微型PCI是PCI2.2版中的新要素,主要用於筆記本電腦的內部。

Cardbus是32位33MHz的PCI,是PCMCIA的要素。

緊湊型PCI,usesEurocard-sizedmodulespluggedintoaPCIbackplane.

PC/104-Plus是一種利用PCI匯流排連線多個連線器的工業匯流排。

高級電訊計算體系(ATCA)是電訊工業下一代匯流排。

匯流排信號

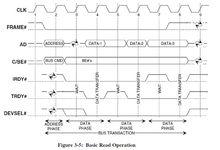

CLK IN:系統時鐘信號,對於所有的PCI設備都是輸入信號。其頻率最高達33MHZ,最小頻率一般為0HZ(DC),這一頻率也稱為PCI的工頻率。對於PCI的其它信號,除了RST#、IRQB#、IRQC#、IRQD#之外,其餘信號都在CLK的上升沿有效(或採樣)。

RST# IN:復位信號。用來使PCI專用的特性暫存器和定序器相關的信號恢復規定的初始狀態。每當復位時,PCI的全部輸出信號一般都應驅動到第三態。SERR#信號為高阻狀態,SBD#和SDONE可驅動到低電平(如果未提供三態輸出)。REQ#和GNT#必須同時驅動到第三態,不能在復位期間為高 或為低。為防止AD、C/BE#及PAR在復位期間浮動,可由中心設備將它們驅動到邏輯低,但不能驅動為高電平。RST#和CLK可以不同步,但要保證其撤消邊沿沒有反彈。

地址和數據信號

AD[31::00] T/S:地址、數據多數復用的輸入/輸出信號。

C/BE[3::0]#T/S:匯流排命令和位元組使能多路復用信號線。在地址期中,這四條線上傳輸的是匯流排命令;在數據期內,它們傳輸的是位元組使能信號,用來表示整個數據期中,AD[31::00]上哪些位元組為有效數據。

PAR T/S:奇偶校驗信號。該信號用於對AD[31::00]和C/BE[3::0]上的信號進行奇偶校驗,以保證數據的準確性。對於地址信號,在地址相位之後的一個時鐘周期PAR穩定有效;對於數據信號,在IRDY#(寫操作)或TRDY#(讀操作)有效之後的一個時鐘周期PAR穩定並有效,一旦PAR有效,它將保持到當前數據相位結束後一個時鐘。在地址相位和寫操作的數據相位,PAR由主設 備驅動,而在讀操作的數據相位,則由從設備驅動。

接口控制信號

FRAME#: S/T/S: 幀周期信號。由當前主設備驅動,表示一次訪問的開始和持續時間。

IRDY# : S/T/S: 主設備準備好信號。在寫周期內該信號有效表示數據已經在[AD::00]中;在讀周期內該信號有效表示主設備已經做好接收數據的準備。

TRDY# : S/T/S: 從設備準備好信號。在寫周期內表示從設備已經做好接收數據的準備;在讀周期內有效,表示數據已經在[AD::00]線上。

STOP# : S/T/S: 停止數據傳送信號。

LOCK#: S/T/S: 鎖定信號。

IDSEL: IN: 初始化設備選擇信號。在參數配置讀寫傳輸期間,用作片選信號。

DEVSEL# S/T/S: 設備選擇信號。該信號有效時,表示驅動它的設備已成為當前訪問的從設備。

PCI仲裁信號

REQ# T/S:匯流排占用請求信號。它是一個點到點的信號線,任何主設備都有其REQ#信號。

GNT# T/S:匯流排占用允許信號。這也是一個點到點的信號線,任何主設備都應有自己的GNT#信號。

PCI錯誤報告信號

PERR# S/T/S: 數據奇偶校驗錯誤報告。但該信號不報告特殊周期中的數據奇偶錯。一個設備只有在回響設備選擇信號(DEVSEL#)和完成數據期之後,才能報告一個PERR#。對於每個數據接收設備,如果發現數據有錯誤,就應在數據收到後的兩個時鐘周期內將PERR#激活。該信號的持續時間與數據期的多少有關,如果是一個數據期於,則最小持續時間為一個時鐘周期;若是一連串的數據期並且每個數據期都有錯,那么PERR#的持續時間將多於一個時鐘周期。由於該信號是持續的三態信號,因此,該信號在釋放前必須先驅動為高電平。另外,對於數據期奇偶錯的報告不能丟失也不能推遲。

SERR# O/D:系統錯誤報告信號。該信號的作用是報告地址奇偶錯、特殊命令序列的數據奇偶錯,以及其它可能引起災難性後果的系統錯誤。

PCI 其它可選信號

SBO# IN/OUT:試探返回信號。

SDONE# IN/OUT:臨聽完成信號。

AD[63::32] T/S:擴展的32位地址和數據多路復用線。

C/BE[7::4]# T/S:匯流排命令和位元組使能多路復用信號線。

REQ64# S/T/S: 64位傳輸請求。

ACK64# S/T/S:64位傳輸認可。

PAR64 T/S:奇偶雙位元組校驗。