簡介

SDRAM

SDRAM同步動態隨機存取記憶體(synchronous dynamic random access memory,簡稱SDRAM)是有一個同步接口的動態隨機存取記憶體(dynamic random access memory,簡稱DRAM)。通常動態隨機存取記憶體(DRAM)是有一個異步接口的,這樣它可以隨時回響控制輸入的變化。而SDRAM有一個同步接口,在回響控制輸入前會等待一個時鐘信號,這樣就能和計算機的系統匯流排同步。時鐘被用來驅動一個有限狀態機,對進入的指令進行流水線操作。這使得SDRAM與沒有同步接口的異步DRAM(asynchronous DRAM)相比,可以有一個更複雜的操作模式。

流水線意味著晶片可以在處理完之前的指令前,接受一個新的指令。在一個寫的流水線中,寫命令在另一個指令執行完之後可以立刻執行,而不需要等待數據寫入存儲佇列的時間。在一個讀的流水線中,需要的數據在讀指令發出之後固定數量的時鐘頻率後到達,而這個等待的過程可以發出其它附加指令。這種延遲被稱為等待時間,在為計算機購買存儲時是一個很重要的參數。

SDRAM在計算機中被廣泛使用,從起初的SDRAM到之後一代的DDR(或稱DDR1),然後是DDR2和DDR3進入大眾市場,而DDR4現在也在籌劃中,預計在2012投入市場。

關係

結構、時序與性能的關係

一、影響性能的主要時序參數

所謂的影響性能是並不是指SDRAM的頻寬,頻率與位寬固定後,頻寬也就不可更改了。但這是理想的情況,在記憶體的工作周期內,不可能總處於數據傳輸的狀態,因為要有命令、定址等必要的過程。但這些操作占用的時間越短,記憶體工作的效率越高,性能也就越好。

非數據傳輸時間的主要組成部分就是各種延遲與潛伏期。通過上文的講述,大家應該很明顯看出有三個參數對記憶體的性能影響至關重要,它們是tRCD、CL和tRP。每條正規的記憶體模組都會在標識上註明這三個參數值,可見它們對性能的敏感性。

以記憶體最主要的操作——讀取為例。tRCD決定了行定址(有效)至列定址(讀/寫命令)之間的間隔,CL決定了列定址到數據進行真正被讀取所花費的時間,tRP則決定了相同L-Bank中不同工作行轉換的速度。現在可以想像一下讀取時可能遇到的幾種情況(分析寫入操作時不用考慮CL即可):

1.要定址的行與L-Bank是空閒的。也就是說該L-Bank的所有行是關閉的,此時可直接傳送行有效命令,數據讀取前的總耗時為tRCD+CL,這種情況我們稱之為頁命中(PH,Page Hit)。

2.要定址的行正好是前一個操作的工作行,也就是說要定址的行已經處於選通有效狀態,此時可直接傳送列定址命令,數據讀取前的總耗時僅為CL,這就是所謂的背靠背(Back to Back)定址,我們稱之為頁快速命中(PFH,Page Fast Hit)或頁直接命中(PDH,Page Direct Hit)。

3.要定址的行所在的L-Bank中已經有一個行處於活動狀態(未關閉),這種現象就被稱作定址衝突,此時就必須要進行預充電來關閉工作行,再對新行傳送行有效命令。結果,總耗時就是tRP+tRCD+CL,這種情況我們稱之為頁錯失(PM,Page Miss)。

顯然,PFH是最理想的定址情況,PM則是最糟糕的定址情況。上述三種情況發生的機率各自簡稱為PHR——PH Rate、PFHR——PFH Rate、PMR——PM Rate。因此,系統設計人員(包括記憶體與北橋晶片)都儘量想提高PHR與PFHR,同時減少PMR,以達到提高記憶體工作效率的目的。

二、增加PHR的方法

顯然,這與預充電管理策略有著直接的關係,目前有兩種方法來儘量提高PHR。自動預充電技術就是其中之一,它自動的在每次行操作之後進行預充電,從而減少了日後對同一L-Bank不同行定址時發生衝突的可能性。但是,如果要在當前行工作完成後馬上打開同一L-Bank的另一行工作時,仍然存在tRP的延遲。怎么辦? 此時就需要L-Bank交錯預充電了。

VIA的4路交錯式記憶體控制就是在一個L-Bank工作時,對下一個要工作的L-Bank進行預充電。這樣,預充電與數據的傳輸交錯執行,當訪問下一個L-Bank時,tRP已過,就可以直接進入行有效狀態了。目前VIA聲稱可以跨P-Bank進行16路記憶體交錯,並以LRU算法進行預充電管理。

有關L-Bank交錯預充電(存取)的具體執行在本刊2001年第2期已有詳細介紹,這裡就不再重複了。

L-Bank交錯自動預充電/讀取時序圖(可點擊放大):L-Bank 0與L-Bank 3實現了無間隔交錯讀取,避免了tRP對性能的影響。

三、增加PFHR的方法

無論是自動預充電還是交錯工作的方法都無法消除tRCD所帶來的延遲。要解決這個問題,就要儘量讓一個工作行在進行預充電前儘可能多的接收多個工作命令,以達到背靠背的效果,此時就只剩下CL所造成的讀取延遲了(寫入時沒有延遲)。

如何做到這一點呢?這就是北橋晶片的責任了。在上文的時序圖中有一個參數tRAS(Active to Precharge Command,行有效至預充電命令間隔周期)。它有一個範圍,對於PC133標準,一般是預充電命令至少要在行有效命令5個時鐘周期之後發出,最長間隔視晶片而異(基本在120000ns左右),否則工作行的數據將有丟失的危險。那么這也就意味著一個工作行從有效(選通)開始,可以有120000ns的持續工作時間而不用進行預充電。顯然,只要北橋晶片不發出預充電(包括允許自動預充電)的命令,行打開的狀態就會一直保持。在此期間的對該行的任何讀寫操作也就不會有tRCD的延遲。可見,如果北橋晶片在能同時打開的行(頁)越多,那么PFHR也就越大。需要強調的是,這裡的同時打開不是指對多行同時定址(那是不可能的),而是指多行同時處於選通狀態。我們可以看到一些SDRAM晶片組的資料中會指出可以同時打開多少個頁的指標,這可以說是決定其記憶體性能的一個重要因素。

Intel 845晶片組MCH的資料:其中表明它可以支持24個頁面同時處於打開狀態

但是,可同時打開的頁數也是有限制的。從SDRAM的定址原理講,同一L-Bank中不可能有兩個打開的行(S-AMP只能為一行服務),這就限制了可同時打開的頁面總數。以SDRAM有4個L-Bank,北橋最多支持8個P-Bank為例,理論上最多只能有32個頁面能同時處於打開的狀態。而如果只有一個P-Bank,那么就只剩下4個頁面,因為有幾個L-Bank才能有同時打開幾個行而互不干擾。Intel 845的MHC雖然可以支持24個打開的頁面,那也是指6個P-Bank的情況下(845MCH只支持6個P-Bank)。可見845已經將同時打開頁數發揮到了極致。

不過,同時打開頁數多了,也對存取策略提出了一定的要求。理論上,要儘量多地使用已打開的頁來保證最短的延遲周期,只有在數據不存在(讀取時)或頁存滿了(寫入時)再考慮打開新的指定頁,這也就是變向的連續讀/寫。而打開新頁時就必須要關閉一個打開的頁,如果此時打開的頁面已是北橋所支持的最大值但還不到理論極限的話,就需要一個替換策略,一般都是用LRU算法來進行,這與VIA的交錯控制大同小異。

規格

晶片和模組

| 標準名稱 | 記憶體時脈 | 周期 | I/O 匯流排時脈 | 數據速率 | 傳輸方式 | 模組名稱 | 極限傳輸率 |

| DDR-200 | 100MHz | 10ns | 100 MHz | 200 Million | 並列傳輸 | PC-1600 | 1600MB/s |

| DDR-266 | 133 MHz | 7.5 ns | 133 MHz | 266 Million | 並列傳輸 | PC-2100 | 2100 MB/s |

| DDR-333 | 166 MHz | 6 ns | 166 MHz | 333 Million | 並列傳輸 | PC-2700 | 2700 MB/s |

| DDR-400 | 200 MHz | 5 ns | 200 MHz | 400 Million | 並列傳輸 | PC-3200 | 3200 MB/s |

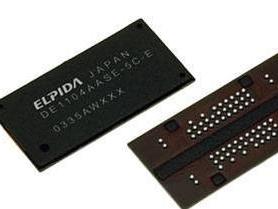

記憶晶片

DDR-200:DDR-SDRAM 記憶晶片在 100MHz 下運行

DDR-266:DDR-SDRAM 記憶晶片在 133MHz 下運行

DDR-333:DDR-SDRAM 記憶晶片在 166MHz 下運行

DDR-400:DDR-SDRAM 記憶晶片在 200MHz 下運行(JEDEC制定的DDR最高規格)

DDR-500:DDR-SDRAM 記憶晶片在 250MHz 下運行(非JEDEC制定的DDR規格)

DDR-600:DDR-SDRAM 記憶晶片在 300MHz 下運行(非JEDEC制定的DDR規格)

DDR-700:DDR-SDRAM 記憶晶片在 350MHz 下運行(非JEDEC制定的DDR規格)

晶片模組

PC-1600記憶體模組指工作在 100MHz 下的DDR-200記憶體晶片,其擁有 1.600GB/s 的頻寬

PC-2100記憶體模組指工作在 133MHz 下的DDR-266記憶體晶片,其擁有 2.133GB/s 的頻寬

PC-2700記憶體模組指工作在 166MHz 下的DDR-333記憶體晶片,其擁有 2.667GB/s 的頻寬

PC-3200記憶體模組指工作在 200MHz 下的DDR-400記憶體晶片,其擁有 3.200GB/s 的頻寬

公式

利用下列公式,就可以計算出DDR SDRAM時脈。

DDR I/II記憶體運作時脈:實際時脈*2。(由於兩邊數據同時傳輸,200MHz記憶體的時脈會以400MHz運作。)

記憶體頻寬=記憶體速度*記憶體位寬

標準公式:記憶體除頻係數=時脈/200→*速算法:外頻*(除頻頻率/同步頻率) (使用此公式將會導致4%的誤差)

取址

(1)bank塊地址---定位邏輯塊

(2)行地址和列地址---定位存儲單元

容量定義

容量定義:地址數*位寬*Bank(存儲塊)。

引腳介紹

SDRAM

SDRAMSDRAM在讀寫數據時重點注意以下信號:

(1)CLK:時鐘信號,為輸入信號。SDRAM所有輸入信號的邏輯狀態都需要通過CLK的上升沿採樣確定。

(2)CKE:時鐘使能信號,為輸入信號,高電平有效。CKE信號的用途有兩個:一、關閉時鐘以進入省電模式;二、進入自刷新狀態。CKE無效時,SDRAM內部所有與輸入相關的功能模組停止工作。

(3)CS#:片選信號,為輸入信號,低電平有效。只有當片選信號有效後,SDRAM才能識別控制器傳送來的命令。設計時注意上拉。

(4)RAS#:行地址選通信號,為輸入信號,低電平有效。

(5)CAS#:列地址選通信號,為輸入信號,低電平有效。

(6)WE#:寫使能信號,為輸入信號,低電平有效。

當然還包括bank[…]地址信號,這個需要根據不同的型號來確定,同樣為輸入信號;地址信號A[…],為輸入信號;數據信號DQ[…],為輸入/輸出雙向信號;數據掩碼信號DQM,為輸入輸出雙向信號,方向與數據流方向一致,高電平有效。當其有效時,數據匯流排上出現的對應數據位元組被接收端禁止。

當今主流

DDR3記憶體。它屬於SDRAM家族的記憶體產品,提供了相較於DDR2 SDRAM更高的運行效能與更低的電壓,是DDR2 SDRAM(四倍資料率同步動態隨機存取記憶體)的後繼者(增加至八倍),也是現時流行的記憶體產品。

DDR3 SDRAM為了更省電、傳輸效率更快,使用了SSTL 15的I/O接口,運作I/O電壓是1.5V,採用CSP、FBGA封裝方式包裝,除了延續DDR2 SDRAM的ODT、OCD、Posted CAS、AL控制方式外,另外新增了更為精進進的CWD、Reset、ZQ、SRT、PASR功能。

CWD是作為寫入延遲之用,Reset提供了超省電功能的命令,可以讓DDR3 SDRAM記憶體顆粒電路停止運作、進入超省電待命模式,ZQ則是一個新增的終端電阻校準功能,新增這個線路腳位提供了ODCE(On Die Calibration Engline)用來校準ODT(On Die Termination)內部中斷電阻,新增了SRT(Self-Reflash Temperature)可程式化溫度控制記憶體時脈功能,SRT的加入讓記憶體顆粒在溫度、時脈和電源管理上進行最佳化,可以說在記憶體內,就做了電源管理的功能,同時讓記憶體顆粒的穩定度也大為提升,確保記憶體顆粒不致於工作時脈過高導致燒毀的狀況,同時DDR3 SDRAM還加入PASR(Partial Array Self-Refresh)局部Bank刷新的功能,可以說針對整個記憶體Bank做更有效的資料讀寫以達到省電功效。

工作原理

SDRAM

SDRAMSDRAM之所以成為DRARM就是因為它要不斷進行刷新(Refresh)才能保留住數據,因此它是DRAM最重要的操作。那么要隔多長時間重複一次刷新,目前公認的標準是,存儲體中電容的數據有效保存期上限是64ms(毫秒,1/1000秒),也就是說每一行刷新的循環周期是64ms。這樣刷新速度就是:行數量/64ms。我們在看記憶體規格時,經常會看到4096RefreshCycles/64ms或8192RefreshCycles/64ms的標識,這裡的4096與8192就代表這個晶片中每個Bank的行數。刷新命令一次對一行有效,傳送間隔也是隨總行數而變化,4096行時為15.625μs(微秒,1/1000毫秒),8192行時就為7.8125μs。HY57V561620為8192refreshcycles/64ms。

SDRAM是多Bank結構,例如在一個具有兩個Bank的SDRAM的模組中,其中一個Bank在進行預充電期間,另一個Bank卻馬上可以被讀取,這樣當進行一次讀取後,又馬上去讀取已經預充電Bank的數據時,就無需等待而是可以直接讀取了,這也就大大提高了存儲器的訪問速度。

為了實現這個功能,SDRAM需要增加對多個Bank的管理,實現控制其中的Bank進行預充電。在一個具有2個以上Bank的SDRAM中,一般會多一根叫做BAn的引腳,用來實現在多個Bank之間的選擇。

SDRAM具有多種工作模式,內部操作是一個複雜的狀態機。SDRAM器件的引腳分為以下幾類。

(1)控制信號:包括片選、時鐘、時鐘使能、行列地址選擇、讀寫有效及數據有效。

(2)地址信號:時分復用引腳,根據行列地址選擇引腳,控制輸入的地址為行地址或列地址。。

(3)數據信號:雙向引腳,受數據有效控制。

SDRAM的所有操作都同步於時鐘。根據時鐘上升沿控制管腳和地址輸入的狀態,可以產生多種輸入命令。

模式暫存器設定命令。

激活命令。

預充命令。

讀命令。

寫命令。

帶預充的讀命令。

帶預充的寫命令。

自動刷新命令。

自我刷新命令。

突發停命令。

空操作命令。

根據輸入命令,SDRAM狀態在內部狀態間轉移。內部狀態包括模式暫存器設定狀態、激活狀態、預充狀態、寫狀態、讀狀態、預充讀狀態、預充寫狀態、自動刷新狀態及自我刷新狀態。

SDRAM支持的操作命令有初始化配置、預充電、行激活、讀操作、寫操作、自動刷新、自刷新等。所有的操作命令通過控制線CS#、RAS#、CAS#、WE#和地址線、體選地址BA輸入。

1、行激活

行激活命令選擇處於空閒狀態存儲體的任意一個行,使之進入準備讀/寫狀態。從體激活到允許輸入讀/寫命令的間隔時鐘節拍數取決於內部特徵延時和時鐘頻率。HY57V561620內部有4個體,為了減少器件門數,4個體之間的部分電路是公用的,因此它們不能同時被激活,而且從一個體的激活過渡到另一個體的激活也必須保證有一定的時間間隔。

2、預充電

預充電命令用於對已激活的行進行預充電即結束活動狀態。預充電命令可以作用於單個體,也可以同時作用於所有體(通過所有體預充電命令)。對於猝發寫操作必須保證在寫入預充電命令前寫操作已經完成,並使用DQM禁止繼續寫入數據。預充電結束後回到空閒狀態,也可以再次被激活,此時也可以輸入進入低功耗、自動刷新、自刷新和模式設定等操作命令。

預充電中重寫的操作與刷新操作一樣,只不過預充電不是定期的,而只是在讀操作以後執行的。因為讀取操作會破壞記憶體中的電荷。因此,記憶體不但要每64ms刷新一次,而且每次讀操作之後還要刷新一次。

3、自動預充電

如果在猝發讀或猝發寫命令中,A10/AP位置為“1”,在讀寫操作完成後自動附加一個預充電動作。操作行結束活動狀態,但在內部狀態機回到空閒態之前不能給器件傳送新的操作命令。

4、猝發讀

猝發讀命令允許某個體中的一行被激活後,連續讀出若干個數據。第一個數據在經過指定的CAS延時節拍後呈現在數據線上,以後每個時鐘節拍都會讀出一個新的數據。猝發讀操作可以被同體或不同體的新的猝發讀/寫命令或同一體的預充電命令及猝發停止命令中止。

5、猝發寫

猝發寫命令與猝發讀命令類似,允許某個體中的一行被激活後,連續寫入若干個數據。第一個寫數據與猝發寫命令同時在數據線上給出,以後每個時鐘節拍給出一個新的數據,輸入緩衝在猝發數據量滿足要求後停止接受數據。猝發寫操作可以被猝發讀/寫命令或DQM數據輸入禁止命令和預充電命令或猝發停止命令中止。

6、自動刷新

SDRAM

SDRAM由於動態存儲器存儲單元存在漏電現象,為了保持每個存儲單元數據的正確性,HY57V561620必須保證在64ms內對所有的存儲單元刷新一遍。一個自動刷新周期只能刷新存儲單元的一個行,每次刷新操作後內部刷新地址計數器自動加“1”。只有在所有體都空閒(因為4個體的對應行同時刷新)並且未處於低功耗模式時才能啟動自動刷新操作,刷新操作執行期間只能輸入空操作,刷新操作執行完畢後所有體都進入空閒狀態。該器件可以每間隔7.8μs執行一次自動刷新命令,也可以在64ms內的某個時間段對所有單元集中刷新一遍。

7、自刷新

自刷新是動態存儲器的另一種刷新方式,通常用於在低功耗模式下保持SDRAM的數據。在自刷新方式下,SDRAM禁止所有的內部時鐘和輸入緩衝(CKE除外)。為了降低功耗,刷新地址和刷新時間全部由器件內部產生。一旦進入自刷新方式只有通過CKE變低才能激活,其他的任何輸入都將不起作用。給出退出自刷新方式命令後必須保持一定節拍的空操作輸入,以保證器件完成從自刷新方式的退出。如果在正常工作期間採用集中式自動刷新方式,則在退出自刷新模式後必須進行一遍(對於HY57V561620來說,8192個)集中的自動刷新操作。

8、時鐘和時鐘禁止

時鐘信號是所有操作的同步信號,上升沿有效。時鐘禁止信號CKE決定是否把時鐘輸入施加到內部電路。在讀寫操作期間,CKE變低後的下一個節拍凍結輸出狀態和猝發地址,直到CKE變高為止。在所有的體都處於空閒狀態時,CKE變低後的下一個節拍SDRAM進入低功耗模式並一直保持到CKE變高為止。

9、DQM操作

DQM用於禁止輸入輸出操作,對於輸出相當於開門信號,對於輸入禁止把匯流排上的數據寫入存儲單元。對讀操作DQM延遲2個時鐘周期開始起作用,對寫操作則是當拍有效。