DCM_Xilinx

FPGA 當中的另一個特殊資源——DCM(數字時鐘管理單元 Digital Clock Manager)。DCM 當中包含一個 DLL(延遲鎖定電路 Delay-Locked Loop),可以提供對時鐘信號的二倍頻和分頻功能,並且能夠維持各輸出時鐘之間的相位關係,即零時鐘偏差。

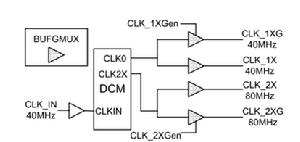

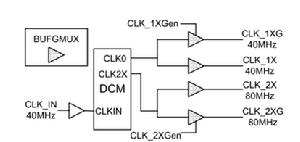

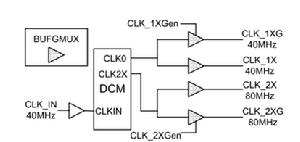

因此,針對分頻時鐘,可以直接利用 DCM 的分頻功能,從而省去分頻暫存器,徹底地解決了 CLK_2X 和 CLK_1X 之間的時鐘偏差。不過更合適的選擇,是使用 DCM 的倍頻功能,這樣只需要為 FPGA 準備一個40MHz 的低頻時鐘輸入,相對 80MHz 來說要更容易實現。

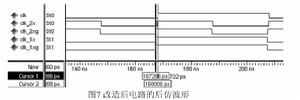

通過 BUFGMUX 和 DCM 的使用可以得到改造後的下圖。 利用DCM改造後的結構圖改造後,每個時鐘域的時鐘信號和信號源 CLK_IN 之間都只通過一個 DCM 和一個BUFGMUX,他們之間的時鐘偏差僅僅為時鐘網路本身的時鐘偏差和 DCM 的輸出到各BUFGMUX 輸入端之間的線路延時偏差。如果進一步最佳化,通過在布局布線的步驟施加對BUFGMUX 的位置約束,迫使4 個 BUFGMUX 都處於 FPGA 的上方或者下方的 8個 BUFGMUX 上,跨時鐘域的時鐘偏差在 VIRTEX-II 6000 FPGA 當中可以控制在 0.5ns以內,基本滿足 80MHz 的要求。改造後的時鐘電路的後仿波形如圖 7 所示,其最大的時鐘偏差為 0.722ns。

利用DCM改造後的結構圖改造後,每個時鐘域的時鐘信號和信號源 CLK_IN 之間都只通過一個 DCM 和一個BUFGMUX,他們之間的時鐘偏差僅僅為時鐘網路本身的時鐘偏差和 DCM 的輸出到各BUFGMUX 輸入端之間的線路延時偏差。如果進一步最佳化,通過在布局布線的步驟施加對BUFGMUX 的位置約束,迫使4 個 BUFGMUX 都處於 FPGA 的上方或者下方的 8個 BUFGMUX 上,跨時鐘域的時鐘偏差在 VIRTEX-II 6000 FPGA 當中可以控制在 0.5ns以內,基本滿足 80MHz 的要求。改造後的時鐘電路的後仿波形如圖 7 所示,其最大的時鐘偏差為 0.722ns。

圖7實際上,DCM 和 BUFGMUX 從 VIRTEX-II 開始,已經成為 FPGA 的標準元件,可以在 SPARTAN-3、VIRTEX-II、VIRTEX-II PRO、VIRTEX-4 等器件上直接使用,因此該電路結構也可相應推廣到這些 FPGA 的電路設計當中。

圖7實際上,DCM 和 BUFGMUX 從 VIRTEX-II 開始,已經成為 FPGA 的標準元件,可以在 SPARTAN-3、VIRTEX-II、VIRTEX-II PRO、VIRTEX-4 等器件上直接使用,因此該電路結構也可相應推廣到這些 FPGA 的電路設計當中。

利用DCM改造後的結構圖

利用DCM改造後的結構圖 圖7

圖7

利用DCM改造後的結構圖

利用DCM改造後的結構圖 圖7

圖7