工作原理

①當一個選通端(E1)為高電平,另兩個選通端((/E2))和(/E3))為低電平時,可將地址端(A0、A1、A2)的二進制編碼在Y0至Y7對應的輸出端以低電平譯出。(即輸出為Y0至Y7的非)比如:A2A1A0=110時,則Y6輸出端輸出低電平信號。

②利用 E1、E2和E3可級聯擴展成 24 線解碼器;若外接一個反相器還可級聯擴展成 32 線解碼器。

③若將選通端中的一個作為數據輸入端時,74LS138還可作數據分配器。

④可用在8086的解碼電路中,擴展記憶體。

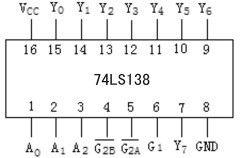

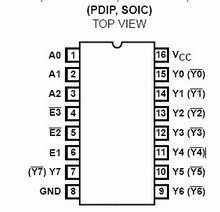

引腳功能

74LS138

74LS138A0~A2:地址輸入端

STA(E1):選通端

/STB(/E2)、/STC(/E3):選通端(低電平有效)

/Y0~/Y7:輸出端(低電平有效)

VCC:電源正

GND:地

A0~A2對應Y0——Y7;A0,A1,A2以二進制形式輸入,然後轉換成十進制,對應相應Y的序號輸出低電平,其他均為高電平;

真值表

| 輸入 | 輸出 | ||||||||||||

| G1 | /G2A | /G2B | A2 | A1 | A0 | /Y0 | /Y1 | /Y2 | /Y3 | /Y4 | /Y5 | /Y6 | /Y7 |

| × | 1 | × | × | × | × | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| × | × | 1 | × | × | × | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | × | × | × | × | × | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |