歐姆接觸

金屬與半導體形成歐姆接觸是指在接觸處是一個純電阻,而且該電阻越小越好,使得組件操作時,大部分的電壓降在活動區(active region)而不在接觸面。因此,其I-V特性是線性關係,斜率越大接觸電阻越小,接觸電阻的大小直接影響器件的性能指標。

歐姆接觸的接觸界面總有一個附加的電阻,即是金屬與半導體間的界面電阻。接觸區一般包括金屬層、金屬與半導體的界面和半導體結。實際測定時,還有各種寄生電阻帶入。為了消除測試時用的探針和金屬間的電阻,可以在測試時將電流和電壓探針分開和使用高阻抗的數字電壓表來達到;但是諸如界面下有電流彎曲、邊緣電流聚集、電流擴展等引入的附加電阻以及工藝過程中的沾污或損傷等引入的電阻,這些附加電阻不可能完全避免。這些附加電阻和兩個接觸點間的體電阻值在所測總電阻值中會占有相當大的比重,甚至可能超過接觸電阻值。為了精確測定比接觸電阻值,需要建立精確的模型來測定電阻值。

研究現狀

20世紀中葉,在世界範圍了掀起了一揚以積體電路的研究與套用為主的電子工業革命。隨後,積體電路集成度與性能的發展基本符合著摩爾定律。隨著對器件需求的不同,半導體器件的發展熱潮逐步由二極體、電晶體、晶閘管、太陽能電池等向著高功率、高頻率、高溫度的器件以及具有特定功能的高精度、高可靠性的MEMS器件發展。所以諸多半導體材料被相繼開發套用,包括Si、SiC、GaAs、GaN等等。至此,不同半導體基底的歐姆接觸研究也就登上了歷史的舞台。

SiC材料的歐姆接觸研究從20世紀50、60年代就已經開始,當時的市場需求相對較小。但是隨著最近部分器件的套用需求趨向高溫、高能、高壓、高頻等方向,而半導體行業中常用的Si與GaAs等由於本身性質的原因而不能勝任。半導體的學穩定性、SiC材料卻具備著一系列的優點,比如寬頻隙、高熱導率、而作為第三代較好的物理化較高的雪崩臨界擊穿電場、較高載流子漂移率、良好的熱穩定性和與外延材料比較好的晶格匹配等等。

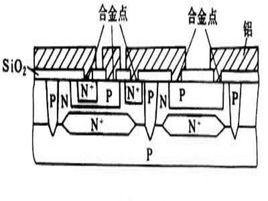

Si材料的歐姆接觸廣泛研究也是從20世紀50、60年代開始。Si作為第一代半導體材料,具有很多優點:其一,在大自然中存在大量的Si元素;其二,具有比較高的熔化溫度,所以不存在工藝熱預算問題;其三,Si工藝日漸成熟;其四,Si很容易被氧化,形成二氧化矽,其性能穩定,在Si製備過程中,可以作為比較好的掩膜層或者絕緣層。基於這么多的優點,Si材料器件被廣泛研究套用,包括pn結二極體、肖特基二極體、電晶體、 CMOS、三極體、晶閘管、場效應管和各種積體電路(晶片和CPU),並且被廣泛用於MEMS/NEMS中。而Si的歐姆接觸在其中充當著電路連線的作用或者根據金屬半導體的接觸能帶特性製備的二極體等等。

相關工藝方式

金屬與半導體的歐姆接觸研究從積體電路工藝發展時就已經開始。對於合適的金屬半導體歐姆接觸的製作,總體上可以分為兩種方式:離子注入與外延。離子注入是從源材料中產生帶正電荷的雜質離子,這些雜質離子經過電場的加速獲得足夠的能量,這樣,雜質離子就能進入到目標晶格中,再經過熱退火的過程,激活這些雜質離子,從而實現基底材料的雜質摻雜。由於離子注入可以精確控制注入雜質的濃度和深度,所以也更加適應器件尺寸越來越小的摩爾定律,所以離子注入在工藝過程中有著不可取代的作用。然而,離子注入也有一些缺點,其一便是高能量的雜質離子轟擊到襯底上,儘管經過退火的修復,仍然會引起晶格損傷;此外,離子注入對雜質離子的高精度控制必然帶來離子注入機的複雜性。外延技術是在襯底上生長一層單晶層,根據向襯底輸送原子的方式基本可以分為三種方式:固相外延(Solid Phase Exitaxy,SPE)、氣相外延(Vapor Phase Exitaxy,VPE)和液相外延(Liquid Phase Exitaxy,LPE)。與離子注入不同的是,根據不同的外延方式,可以選擇不同的儀器或者方法來進行外延,比如針對VPE的方式,可以採用不同的氣相反應爐或者一些CVD儀器,而對於LPE的方式而言,我們就可以採取液相反應爐或者合金的方式等等。所以,相對離子注入方式而言,外延的設備相對簡單而且對於襯底的損傷也要小很多。