基本概念

數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決於該時刻的輸入,與電路原來的狀態無關。而時序邏輯電路在邏輯功能上的特點是任意時刻的輸出不僅取決於當時的輸入信號,而且還取決於電路原來的狀態,或者說,還與以前的輸入有關。

時序邏輯電路其任一時刻的輸出不僅取決於該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯元件有觸發器、計數器、暫存器等。由於時序邏輯電路具有存儲或記憶的功能,檢修起來就比較複雜。

計數器

計數器功能:統計輸入脈衝的個數。

計數器除了直接用於計數外,還可以用於定時器、分頻器、程式控制器、信號發生器等多種數字設備中。

按計數器中的觸發器是否同時翻轉分類:同步計數器、異步計數器。

按計數器中數字的編碼方式分類:二進制計數器、非二進制計數器。

異步計數器

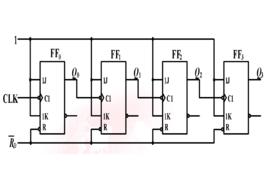

電路組成和邏輯功能分析:

時序邏輯元件

時序邏輯元件二進制加法計數規則:如果低位已經為1,則再記入1時就應回到0,同時向高位送出進位信號。因此,只要將T'觸發器從1變加時輸出端電位的跳變做為進位信號,並接至高一位觸發器的時鐘輸入端,就可以得到多位二進制加法計數器了。

異步二進制計數器的特點:

(1)異步二進制計數器可由T'觸發構成,觸發器之間串接低位觸發器的輸出,作為高位觸發器的時鐘。

(2)由於觸發器的狀態翻轉是由低位向高位逐級進行的,因此,計數速度較低。

時序邏輯元件

時序邏輯元件 時序邏輯元件

時序邏輯元件 時序邏輯元件

時序邏輯元件 時序邏輯元件

時序邏輯元件 時序邏輯元件

時序邏輯元件 時序邏輯元件

時序邏輯元件(3)若CLK脈衝的頻率為f,則 ~ 輸出脈衝的頻率 、 、 、 。常稱這種計數器為分頻器。

同步計數器

根據計數器的功能要求,n位二進制計數器用n個存儲單元電路組成,存儲單元的狀態表示二進制數,存儲單元由觸發器實現;輸入脈衝將使各位觸發器的狀態按計數規律變化,即每輸入一個脈衝,由觸發器的狀態表示的二進制數必須加1。

由於是同步計數器,輸入脈衝將同步加到各觸發器的時鐘輸入端,因此只有通過控制觸發器的驅動信號來達到控制觸發器狀態的目的。

同步二進制加法計數器的特點:

時序邏輯元件

時序邏輯元件(1)由n個觸發器構成的同步二進制加法計數器的模為 ,沒有多餘狀態,利用率最高;

(2)用T觸發器構成的同步二進制加法計數器,其電路結構有兩條規則:

時序邏輯元件

時序邏輯元件 時序邏輯元件

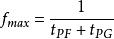

時序邏輯元件(3)同步計數器工作速度快,這種計數器的最高工作頻率可達:

時序邏輯元件

時序邏輯元件暫存器和移位暫存器

暫存器

暫存器用途:暫時存放二進制數碼。

暫存器作為一個邏輯部件來使用,一般都包含有觸發器堆和控制電路兩個部分。

移位暫存器

功能:存放代碼、移位。

移位暫存器組成:移位暫存器中的存儲電路可用時鐘控制的無空翻的D、RS或JK觸發器組成。

觸發器

觸發器為同步操作時序邏輯元件,其輸出由輸入時鐘所規定的時刻的數據輸入確定。因此,可將時鐘想像為對數據採樣的控制,即在由時鐘轉換所確定的時刻,對數據進行採樣。由此可見,觸發器應屬於時鐘驅動元件,這是同步時序電路由時鐘實現同步控制的基礎。對於觸發器的綜合有如下規則:

(1)每一個同步賦值的信號對應一個觸發器。

(2)如果同步賦值語句中的目標變數在未賦值之前就被使用,則該變數可對應一個觸發器;否則,其只是作為中間數據的暫存,不產生硬體元件。

(3)一個同步賦值中的目標變數或目標信號不能在其它賦值語句中被賦值,但是,一個向量的單個元素可以分別處理。

(4)每個進程只允許有一個時鐘.

(5)賦值的目標信號與目標變數的綜合方法不同:

a.信號的時序賦值可綜合為觸發;

b.變數的時序賦值,只有當變數在賦值之前讀取時才採用觸發器;否則,不採用觸發器 。