異步復位信號

優點

1)識別方法簡單,可用於全局復位

2)設計相對簡單,不需要額外的邏輯資源,易於實現

3)大多數器件庫中的器件都有異步復位連線埠,可節省資源

缺點

1)在復位信號釋放的時候容易出現問題,若復位剛好在時鐘有效沿附近釋放,很容易使暫存器輸出端出現亞穩態

2)異步復位易觸發,容易受到毛刺的影響,所以對異步復位源要求較高

3)難以進行靜態時序分析,難以仿真

復位信號重要性

隨著積體電路設計技術的發展,單晶片電路的設計規模越來越大,設計複雜度也相應地越來越高。

目前,在積體電路設計中,特別是以SoC晶片(System on chip片上系統)為代表的大規模積體電路設計中,通常都採用同步時序設計方法。即晶片內部的所有觸發器都工作於相同的時鐘信號,而且觸發器狀態的翻轉也都發生在同一時刻。

同步時序設計方法要求晶片內部時鐘信號到達晶片內部各個觸發器的時間一致。實際上,由於時鐘信號到達各個觸發器所經歷路徑的不同,將會導致各個觸發器上時鐘信號的延時都不太一致。為了保證時鐘沿到達各個觸發器的時間相同,設計人員通常需要對時鐘經歷的各個路徑時進行補償,即進行時鐘樹的平衡。

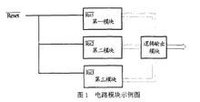

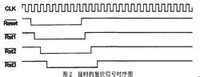

同樣的,在晶片復位電路的設計中,復位信號的延時也將會對電路的數字邏輯產生影響。如圖1所示的電路,由於三個不同的電路模組的復位信號輸入端(Rst)與整個晶片的復位信號源(Reset)的電路

連線路徑不同,就有可能造成如圖2所示的復位信號延時。當復位信號不同步時,由於各模組的輸出還有後續的邏輯運算,就有可能造成在模組1的復位信號消失並開始運轉的時刻,模組2和模組3的復位操作仍然沒有完成,其輸出還處於不確定狀態,從而導致系統邏輯狀態混亂的不良結果。

復位信號

復位信號 復位信號

復位信號