簡介

為了能將用戶地址空間中的邏輯地址變換為記憶體空間中的物理地址,在系統中必須設定地址變換機構。該機構的基本任務是實現從邏輯地址到物理地址的轉換。由於頁內地址和物理地址是一一對應的(例如,對於頁面大小是 1 KB 的頁內地址是 0~1023,其相應的物理塊內的地址也是 0~1023,無須再進行轉換),因此,地址變換機構的任務實際上只是將邏輯地址中的頁號,轉換為記憶體中的物理塊號。在地址變換機構中,一般通過查詢和對比地址變換表中地址,來實現虛地址到實地址的轉換。在地址變換機構中,地址變換表引入,加快了地址映射速度和減少有效訪問時間。在作業系統中地址變換表可以分為頁表(慢表)和快表。

地址轉換

通常,中央處理器給出的訪存地址是邏輯地址(或虛地址),它必須由地址轉換機構轉換成物理地址後才能訪問主存。為了減少高速快取訪問的命中時間(它決定中央處理器的時鐘周期 ),許多系統採用了虛地址高速快取這類高速快取中的地址標誌是虛地址,中央處理器給出的地址不經轉換就可用於高速快取訪問,而同時該地址可由地址轉換機構轉換成物理地址從而一旦高速快取不命中,可立即用實地址訪問主存。虛地址高速快取帶來的一個問題是,當進程切換時必須清除高速快取因為不同進程的虛地址空間都是一樣的。這對系統 (尤其是需要對上下文頻繁切換的事務處理系統)性能有一定的影響。另外,考慮到程式訪問指令和數據的不同特點,可以設定專門存放指令和專門存放數據的高速快取它們可採用不同的容量和策略。指令和數據分開存放有利於指令流水線的實現。

快慢表

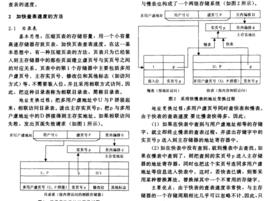

頁表是一種特殊的數據結構,放在系統空間的頁表區,存放邏輯頁與物理頁幀的對應關係。 每一個進程都擁有一個自己的頁表,PCB表中有指針指向頁表。基本思想:大大縮小目錄表的存儲容量,從而大大加快查錶速度。在這種基本思想中,考慮到程式在執行過程中具有局限性,因此,對頁表中各存儲字的訪問並不是完全隨機的。也就是說在一段時間內,對頁表訪問只是局限在少數幾個存儲字內。把經常訪問的頁表放在一個小容量高速存儲器中,稱為快表TLB(Translation Lookaside Buffer),小容量(幾十個字),高速硬體實現,採用相聯方式訪問 。不經常訪問的頁表放在主存儲器中,稱為慢表,按地址訪問,用軟體實現。快表地址變換過程:多用戶虛頁號同時查快表和慢表。由於快表的查錶速度要比慢錶快得多,因此:

如果在快表中查到與用戶虛地址相等的存儲字,就立即終止慢表的查表過程,並讀出存儲字中的實頁號p送人到主存儲器的地址暫存器中。

如在快表中沒有查到,就到慢表中去查找。如果在慢表中查到了,則把查到的實頁號p送人主存儲器的地址暫存器,同時也把這個實頁號連同多用戶虛地址等信息送人快表中。這時,若快表已滿,則要採用某種替換算法。替換掉其中一個不常用的存儲字。

主要優點:由於快表的查錶速度非常快,與主存儲器的一個存儲周期相比幾乎可以忽略不計。因此,只要快表的命中率很高,那么,虛擬存儲器的訪問速度就能主存儲器的工作速度很接近。

主要缺點:要提高快表的命中率,最直接的辦法是增加快表的容量。但是,由於快表是相聯方式訪問的當快表容量增加時,他的查錶速度就會降低 。