概述

FIFO是一種特殊功能的暫存器,數據以到達FIFO輸入連線埠的先後順序存儲在存儲器中,並以相同的順序從FIFO的輸出連線埠送出,所以FIFO內數據的寫入和讀取只受讀/寫請求信號的控制,而不需要讀/寫地址線。

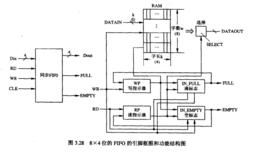

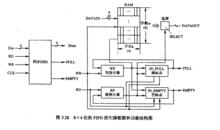

FIFO是先進先出棧,作為數據緩衝器,通常其數據存放結構是完全和RAM一致的,只是存取方式不同。圖中是容量為8×4位的FIFO的引腳框圖和功能結構圖。圖中的FIFO有4條數據輸入線Din,4條數據輸出線Dout,一條讀控制線RD,一條寫控制線WR,一條時鐘輸入線CLK及兩條狀態信號線,即滿信號和空信號線(FULL,EMPTY)。

先進先出棧

先進先出棧結構

FIFO由6個功能塊組成,它們是存儲體,寫指示器(WP),讀指示器(RP),滿標誌IN_FULL,空標誌IN_EMPTY和選擇邏輯SELECT。這是一個同步的FIFO。在時鐘脈衝上升沿作用下,當WR=0且FULL=0時,Din的數據將進入FIFO棧。在通常情況下,RP指示器所指出的單元內容總是放於Dout的輸出數據線上,只是在RD=0且EMPTY=0時,RP指示器內容才改變而指向FIFO的下一個單元,下一個單元的內容替換當前內容並從Dout輸出。

需要注意的是,在任何時候Dout上有1個數據輸出,而不像RAM那樣,只有在讀有效時才有數據輸出,平時為三態輸出。

先進先出棧

先進先出棧FIFO的存儲器實際上是一個環形數據結構,由WP和RP分別指示數據寫和讀的對應單元。在這裡WP指的是新數據待寫入的單元地址,發一個WR有效信號(WR=‘0’)就可將Din上的數據寫入該單元;而RP指的是已讀出數據的單元地址,要想讀下一個數據就要發一個RD有效信號(RD=‘0’),使RP=RP+1,這時就可以讀出下一個新的數據了。RP和WP之間的信號關係如圖所示。

FIFO在復位以後就處於初始狀態。WP=0,RP=7,此時FIFO處於空狀態,數據第一次寫入的單元應該是0號單元。RP和WP之間應該滿足RP=WP-1。RP=WP狀態是FIFO

只要進行一次寫操作就會變成滿的狀態。連續寫7個數據以後就會變成RP=WP=7,此時若再寫一個數據就會使FIFO變成滿狀態。RP=WP一2狀態時,只要再讀一次,就會使FIFO變成空狀態。滿狀態和空狀態的RP和WP的關係是一致的,均是RP=WP-1。但是,滿狀態和空狀態出現之前的一個狀態是各不相同的。在RP=WP時,由於寫一個數據而使其進入滿狀態(RP=WP一1);在RP=WP一2時,由於讀一個數據而使其進入滿狀態(RP=WP-1)。據此,即可得到滿或空信號產生的條件。