基本概念

乘法器在當今數位訊號處理以及其他諸多套用領域中起著十分重要的作用。隨著科學技術的發展,許多研究人員已經開始試圖設計一類擁有更高速率和低功耗,布局規律占用面積小,集成度高的乘法器。這樣,就能讓它們更加適用於高速率,低功耗的大規模積體電路的套用當中。

乘法器(multiplier)是一種完成兩個互不相關的模擬信號相乘作用的電子器件。它可以將兩個二進制數相乘。它是由更基本的加法器組成的。通常的乘法計算方法是添加和位移的算法。在並行乘法器當中,相加的部分乘積的數量是主要的參數。它決定了乘法器的性能。為了減少相加的部分乘積的數量,修正的Booth算法是最常用的一類算法。為了實現速度的提高Wallace樹算法可以用來減少序列增加階段的數量。我們進一步結合修正的booth算法和Wallace樹算法,可以看到將它們集成到一塊乘法器上的諸多優勢。但是,隨著並行化的增多,大量的部分乘積和中間求和的增加,會導致運行速度的下降。不規則的結構會增加矽板的面積,並且由於路由複雜而導致中間連線過程的增多繼而導致功耗的增大。另一方面串並行乘法器犧牲了運行速度來獲得更好的性能和功耗。因此,選擇一款並行或串列乘法器實際上取決於它的套用性質 。

乘法器

乘法代價很高並且運算很慢。許多計算問題的性能常常是由乘法運算所能執行的速度決定的。這一事實已促使設計者將整個乘法單元集成在例如現代數位訊號處理器和微處理器中。

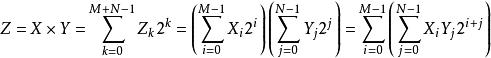

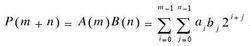

乘法器事實上就是一個複雜的加法器陣列考慮兩個沒有符號的二進制數X和Y甲分別為M位寬和N位寬。為獷說明乘法運算,可以用二進制形式來表示X和Y:

乘法電路

乘法電路 乘法電路

乘法電路乘法運算定義如下:

乘法電路

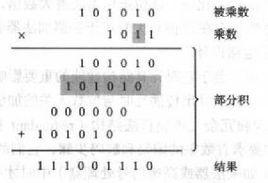

乘法電路執行一個乘法運算最簡單的是採用一個兩輸入的加法器。對於M和N位寬的輸 ,乘法採用一個N位加法器時需要M個周期。這個乘法的移位和相加算法把M個部分積(partial product)加在一起。每一個部分積是通過將被乘數與乘數的一位相乘(這本質上是一個“與”操作),然後將結果移位到這個乘數位的位置得到的。

實現乘法的一個更快的辦法是採用類似於手工計算乘法的方法。所有的部分積同時產生並組成一個陣列,運用多運算元相加來汁算最終的積。這一方法如圖所示:

乘法電路

乘法電路這一組操作可以直接映射到硬體;所形成的結構稱為陣列乘法器(array multiplier),它結合了下面三個功能:產生部分積,累加部分積和最終相加 。

乘運算

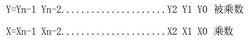

對於一個N比特的被乘數和一個N比特的乘數相乘的算法如下圖所示:

乘法電路

乘法電路一般來說

乘法電路

乘法電路“與”門被用來產生部分乘積,如果被乘數是N比特,乘數是M比特,那么就會產生N*M個部分積,然而在不同結構和類型的乘法器當中,部分乘積的產生方式是不同的。 二進制的乘法可以被分解為加法。現考慮兩個八比特的二進制數A和B相乘產生一個16比特的數。如下圖:

乘法電路

乘法電路滿足這一方程:

乘法電路

乘法電路乘算法如下:

如果A的最低有效位是1,那么將B加到累加器中。

將A右移一比特,那么B左移了一比特。

當A的所有比特為0時停止。

從上面可以清晰地看出,數乘已經被轉換成了加法運算。如果部分乘積被連續相加,因此一個串列加法器就可以和硬體一起使用。在組合電路中通過並行乘法器將所有的部分乘積相加是可以行的通的。然而,通過使用壓縮技術,可以將部分乘積的數量降低。從這方面,是可以進行的。

乘法器類型

串/並行乘法器

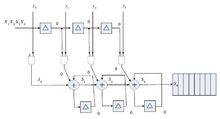

一般結構的串/並行乘法器的結構如下圖。將一個運算元並行送入電路中,而另一個數則串列輸入。N個部分乘積組成每一個循環。在連續循環中,每一個循環結果作為M*N的乘法陣列的一列相加結果。最後的結果在2N個循環之後儲存到輸出暫存器當中。

乘法電路

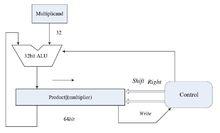

乘法電路位移和添加乘法器

位移和添加乘法器的一般結構如下圖所示,對於32比特的數乘運算,根據乘數最低有效位的數值,被乘數的數值被相加並累積。在每一個時鐘循環周期內,乘數被左移一個比特,並且它的位值被測試,如果位值是0,則只進行一次位移操作。如果位值是1,則被加數被放入累加器中,並且左移一位。當所有乘數的比特值被測試完之後,結果就在累加器當中。累加器最初是N位,相加之後變成2N位,最低有效位包涵了乘數。延遲是N個最大循環周期。這類電路放在異步電路中有許多好處。

乘法電路

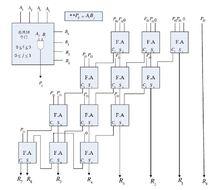

乘法電路陣列乘法器

陣列乘法器因它規則的結構被大家熟知。乘法器電路是基於加法和位移的算法。每一個部分乘積是由被乘數和一個乘數比特相乘得到的。部分乘積根據它們的比特排列產生位移然後相加。整個相加過程可以在進位傳輸加法器當中完成。整個系統需要N-1個加法器並要求有乘數的長度。

這種計算方法是很簡單的,加法在系統中是連續並行處理的。為了減小延遲和占用面積。逐位進位加法器可以用進位保留加法器取代。這樣的話,每一個進位和求和信號都可以在下一個階段通過加法器。最終的結果在最末端的加法器中獲取。在陣列乘法器中我們需要相加的部分乘積要和乘數的比特數一樣多。這種排列如下圖所示:

乘法電路

乘法電路