簡介

Virtex是Xilinx FPGA中的高端產品,占據著全球高端產品的大部分市場,從Virtex-II開始,這一系列產品不斷升級和更新,性能也越來越卓越。Xilinx於2011年推出了最新的Virtex-7。

資源

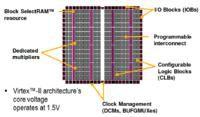

以Virtex-II為例說明器件結構及內部資源。Virtex-II內部資源包括RAM,乘法器,IOB,可程式互聯線,數字時鐘管理器DCM和可程式邏輯陣列CLB。

CLB: 每個CLB包括開關陣列、 4個slice、兩條單獨的進位鏈及本地布線資源。slice包含了基本的邏輯單元,開關陣列用於同基本的布線資源相連線,本地互聯線用於連線內部slice以及相鄰CLB中的slice。

slice:slice是XilinxFPGA中的基本邏輯單元,在一般的設計中,邏輯資源的使用情況用已使用的slice的個數來衡量。每個slice包括兩個四輸入查找表(LUT)、一條進位鏈以及兩個暫存器,還包括一些多路選擇器。

multiplier:乘法器輸入位寬為18bit,輸出36bit,每個18*18的乘法器可作為2個9*9乘法器使用。在晶片內部,乘法器和內嵌RAM是相鄰的。

IOB:輸入:2個DDR暫存器。輸出:2個DDR暫存器、兩個3態使能DDR暫存器。輸入輸出有單獨的時鐘和使能,共享復位和置位信號。提供可選的電平標準: LVTTL, LVCMOS (3.3V, 2.5V, 1.8V,1.5V)、 PCI-X (133 MHz)PCI (3.3V 33 MHz & 66 MHz)、GTL、GTLP等。 RAM:雙連線埠RAM,每個連線埠擁有同步的讀寫使能,兩個連線埠有使用單獨的時鐘,在器件內部,RAM與乘法器相鄰,以獲得更高速度。

DCM:每個器件多達12個DCM,分布在頂部和底部的邊緣,提供DLL,DFS,DPS。DCM輸出能直接驅動互聯線。