定義

l導體中含有許多可以自由移動的電子,而絕緣體中電子被束縛在自身所屬的原子核周圍,這些電子可以相互交換位置,但是不能到處移動。絕緣體不能導電,但電場可以在其中存在,並且在電學中起著重要的作用。因此從電場的角度來看,絕緣體也被稱為電介質(dielectric)。 正如導體一樣,電介質在電子工程領域有著廣泛套用,電容器內的儲電材料以及晶片內的絕緣材料等都是電介質。

為了定量分析電介質的電氣特性,用介電常數k(permittivity或dielectric constant)來描述電介質的儲電能力。 電容C定義為儲存的電量Q與電壓E的比值,在相同電壓下,儲存的電量越多,則說明電容器的容量越大。電容的容量與電容器的結構尺寸及電介質的k值有關(圖1),其中作為儲電材料的電介質的k 值對電容容量的大小起著關鍵性作用,製造大容量的電容器時通常是通過選擇高k 值的電介質來實現的。

不同電介質的介電常數k 相差很大,真空的k 值為1,在所有材料中最低;空氣的k值為1.0006;橡膠的k值為2.5~3.5;純淨水的k值為81。工程上根據k值的不同,把電介質分為高k(high-k)電介質和低k(low-k)電介質兩類。介電常數k >3.9 時,判定為high-k;而k≤3.9時則為low-k。IBM將low-k標準規定為k≤2.8,目前業界大多以2.8作為low-k電介質的k 值上限。

作用

low-k

low-k在積體電路內部,由於ILD(Inter Layer Dielectrics,層間電介質)的存在,導線之間就不可避免地存在分布電容,或者稱之為寄生電容(圖2)。分布電容不僅影響晶片的速度,也對工作可靠性構成嚴重威脅。從電容器容量計算公式中我們可以看出,在結構不變的情況下,減少電介質的k值,可以減小電容的容量。因此,使用low-k電介質作為ILD,可以有效地降低互連線之間的分布電容,從而可使晶片總體性能提升10%左右。

縮短了信號傳播延時

low-k

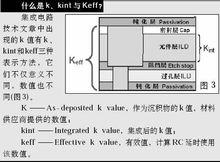

low-k積體電路的速度由電晶體的柵延時(Gate Delay)和信號的傳播延時(Propagation Delay)兩個參數共同決定,延時時間越短,信號的頻率越高。 柵延時主要是由MOS管的柵極材料所決定,使用high-k材料可以有效地降低柵延時。傳播延時也稱為RC延時(RC delay),R是金屬導線的電阻,C是內部電介質形成的電容。RC 延時的表達式為: TRC=ρε(L2/TD) 注:公式中ρ為金屬的電阻率,ε(也記做k)是電介質的介電常數,L 為導線長度,T 是電介質厚度,D為金屬導線厚度。 該公式反映了電路參數對TRC 的影響,公式中雖沒有出現電阻R和電容C兩個符號,但又都與這兩個參數有關。電阻率ρ、導線的長度L、導線厚度D 三個參數與電阻R 有關,而介電常數ε、導線長度L 兩個參數與電容C 的大小有關。

low-k

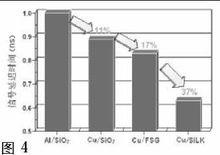

low-k金屬材料和絕緣材料對傳播延時都會產生影響(圖4)。由於銅(Cu)導線比鋁(Al)導線的電阻更低,FSG比SiO2的k值低,所以,銅互連與low-k工藝的同時套用,將使得傳播延時變得越來越短了。

降低了線路串擾

low-k

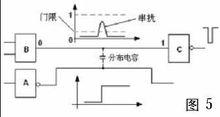

low-k當一條傳輸線傳送信號時,通過互感(磁場)在另一條傳輸線上產生感應信號,或者通過電容(電場)產生耦合信號,這兩種現象統稱為串音干擾,簡稱“串擾(crosstalk)”。串擾可使相鄰傳輸線中出現異常的信號脈衝,造成邏輯電路的誤動作(圖5)。耦合串擾是由導線間的寄生電容引起的,根據容抗表達式XC=1/2πfC可知:電容的容量C越大,XC越小,信號越容易從一根導線穿越電介質到達另一根導線,線路間的串擾就越嚴重;信號的頻率f越高,脈衝的上升、下降時間越短,串擾也越嚴重。 由於CPU速度不斷攀升,信號頻率f目前已超過3GHz。但是,線路串擾已經成為進一步提高頻率的限制條件,晶片 技術的發展面臨巨大挑戰。鑒於k值與分布電容之間的因果關係,尋求k值更低的ILD材料,最大程度地降低串擾影響,是保持晶片微型化和高速化發展的一個有效途徑。 從上面的分析可以得出兩個結論:首先,晶片中使用low-k電介質作為ILD,可以減少寄生電容容量,降低信號串擾,這樣就允許互連線之間的距離更近,為提高晶片集成度掃清了障礙;其次,減小電介質k值,可以縮簡訊號傳播延時,這樣就為提高晶片速度留下了一定空間。

優缺點

電介質作為晶片必備的一種材料,除了低k值外,電介質材料至少應具備以下三個方面的特性:絕緣性能好、導熱性好、便於製造。進入90nm工藝後,low-k電介質的開發和套用是晶片廠商面臨的難題。 由於low-k材料的抗熱性、化學性、機械延展性以及材料穩定性等問題都還沒有得到完全解決,給晶片的製造和質量控制帶來很多困難。採用low-k材料後,多家晶片大廠的產品都出現過不同程度的問題。 與SiO2相比,low-k材料密度較低,這樣帶來兩個問題,一是熱傳導性能較差,不利於晶片內熱量的散發,由此導致晶片熱穩定性變壞;二是銅更容易擴散進入絕緣層材料的孔隙中,不僅影響了互連的可靠性,如果不採取適當防擴散工藝措施,情況嚴重時會因電介質中銅含量過高而帶來漏電和功耗升高問題。雖然電流泄露途徑主要是“柵泄漏(Gate leakage)”,但“電介質泄漏(Dielectric leakage)”問題也同樣不可忽視。在製造工藝上,由於low-k材料的鬆軟結構和易滲透性,使得CMP(化學機械研磨)和清潔工序變得更為艱難,並導致成品率下降和生產成本的提高。