接口

JTAG最初是用來對晶片進行測試的,JTAG的基本原理是在器件內部定義一個TAP(Test Access Port;測試訪問口)通過專用的JTAG測試工具對內部節點進行測試。JTAG測試允許多個器件通過JTAG接口串聯在一起,形成一個JTAG鏈,能實現對各個器件分別測試。如今,JTAG接口還常用於實現ISP(In-System Programmer,在系統編程),對FLASH等器件進行編程。

JTAG編程方式是線上編程,傳統生產流程中先對晶片進行預編程然後再裝到板上,簡化的流程為先固定器件到電路板上,再用JTAG編程,從而大大加快工程進度。JTAG接口可對DSP晶片內部的所有部件進行編程。

JTAG引腳定義

具有JTAG口的晶片都有如下JTAG引腳定義:

TCK——測試時鐘輸入;

TDI——測試數據輸入,數據通過TDI輸入JTAG口;

TDO——測試數據輸出,數據通過TDO從JTAG口輸出;

TMS——測試模式選擇,TMS用來設定JTAG口處於某種特定的測試模式。

可選引腳TRST——測試復位,輸入引腳,低電平有效。

含有JTAG口的晶片種類較多,如CPU、DSP、CPLD等。

JTAG內部有一個狀態機,稱為TAP控制器。TAP控制器的狀態機通過TCK和TMS進行狀態的改變,實現數據和指令的輸入。

JTAG晶片的邊界掃描暫存器

JTAG標準定義了一個串列的移位暫存器。暫存器的每一個單元分配給IC晶片的相應引腳,每一個獨立的單元稱為BSC(Boundary-Scan Cell)邊界掃描單元。這個串聯的BSC在IC內部構成JTAG迴路,所有的BSR(Boundary-Scan Register)邊界掃描暫存器通過JTAG測試激活,平時這些引腳保持正常的IC功能。

JTAG線上寫Flash的硬體電路設計

JTAG線上寫Flash的硬體電路設計和與PC的連線方式

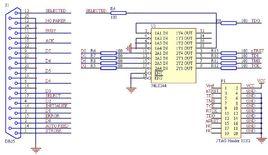

以含JTAG接口的StrongARM SA1110為例,Flash為Intel 28F128J32 16MB容量。SA1110的JTAG的TCK、TDI、TMS、TDO分別接PC並口的2、3、4、11線上,通過程式將對JTAG口的控制指令和目標代碼從PC的並口寫入JTAG的BSR中。在設計PCB時,必須將SA1110的數據線和地址線及控制線與Flash的地線、數據線和控制線相連。因SA1110的數據線、地址線及控制線的引腳上都有其相應BSC,只要用JTAG指令將數據、地址及控制信號送到其BSC中,就可通過BSC對應的引腳將信號送給Flash,實現對Flash的操作。JTAG的系統板設計和連線關係如圖3所示。

使用TAP狀態機的指令實行對Flash的操作

通過TCK、TMS的設定,可將JTAG設定為接收指令或數據狀態。JTAG常用指令如下:

SAMPLE/PRELOAD——用此指令採樣BSC內容或將數據寫入BSC單元;

EXTEST——當執行此指令時,BSC的內容通過引腳送到其連線的相應晶片的引腳,我們就是通過這種指令實現線上寫Flash的;

BYPASS——此指令將一個一位暫存器置於BSC的移位迴路中,即僅有一個一位暫存器處於TDI和TDO之間。

在PCB電路設計好後,即可用程式先將對JTAG的控制指令,通過TDI送入JTAG控制器的指令暫存器中。再通過TDI將要寫的Flash的地址、數據及控制線信號寫入BSR中,並將數據鎖存到BSC中,用EXTEST指令通過BSC將寫入Flash。

軟體編程

線上寫Flash的程式用Turbo C編寫。程式使用PC的並行口,將程式通過含有JTAG的晶片寫入Flash晶片。程式先對PC的並口初始化,對JTAG口復位和測試,並讀Flash,判斷是否加鎖。如加鎖,必須先解鎖,方可進行操作。寫Flash之前,必須對其先擦除。將JTAG晶片設定在EXTEST模式,通過PC的並口,將目標檔案通過JTAG寫入Flash,並在燒寫完成後進行校驗。程式主流程如圖4所示。

通過JTAG的讀晶片ID子程式如下:

電路設計和編程中的注意事項

①Flash晶片的WE、CE、OE等控制線必須與SA1110的BSR相連。只有這樣,才能通過BSR控制Flash的相應引腳。

②JTAG口與PC並口的連線線要儘量短,原則上不大於15cm。

③Flash在擦寫和編程時所需的工作電流較大,在選用系統的供電晶片時,必須加以考慮。

④為提高對Flash的編程速度,儘量使TCK不低於6MHz,可編寫燒寫Flash程式時實現。

說明

通常所說的JTAG大致分兩類,一類用於測試晶片的電氣特性,檢測晶片是否有問題;一類用於Debug,一般支持JTAG的CPU內都包含了這兩個模組。

一個含有JTAG Debug接口模組的CPU,只要時鐘正常,就可以通過JTAG接口訪問CPU的內部暫存器和掛在CPU匯流排上的設備,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)內置模組的暫存器,像UART,Timers,GPIO等等的暫存器。

上面說的只是JTAG接口所具備的能力,要使用這些功能,還需要軟體的配合,具體實現的功能則由具體的軟體決定。

例如下載程式到RAM功能。了解SOC的都知道,要使用外接的RAM,需要參照SOC DataSheet的暫存器說明,設定RAM的基地址,匯流排寬度,訪問速度等等。有的SOC則還需要Remap,才能正常工作。運行Firmware時,這些設定由Firmware的初始化程式完成。但如果使用JTAG接口,相關的暫存器可能還處在上電值,甚至是錯誤值,RAM不能正常工作,所以下載必然要失敗。要正常使用,先要想辦法設定RAM。在ADW中,可以在Console視窗通過Let 命令設定,在AXD中可以在Console視窗通過Set命令設定。

定義

JTAG(Joint Test Action Group ,聯合測試行動小組 ) 是一種國際標準測試協定,主要用於晶片內部測試及對系統進行仿真、調試, JTAG 技術是一種嵌入式調試技術,它在晶片內部封裝了專門的測試電路 TAP ( Test Access Port ,測試訪問口),通過專用的 JTAG 測試工具對內部節點進行測試。

如今大多數比較複雜的器件都支持 JTAG 協定,如 ARM 、 DSP 、 FPGA 器件等。標準的 JTAG 接口是 4 線: TMS 、 TCK 、 TDI 、 TDO ,分別為測試模式選擇、測試時鐘、測試數據輸入和測試數據輸出。如今 JTAG 接口的連線有兩種標準,即 14 針接口和 20 針接口,其定義分別如下所示。

14針

1 、 13 VCC 接電源

2 、 4 、 6 、 8 、 10 、 14 GND 接地

3 nTRST 測試系統復位信號

5 TDI 測試數據串列輸入

7 TMS 測試模式選擇

9 TCK 測試時鐘

11 TDO 測試數據串列輸出

12 NC 未連線

20針

1 VTref 目標板參考電壓,接電源

2 VCC 接電源

3 nTRST 測試系統復位信號

4、6、8、10、12、14、16、18、20 GND 接地

5 TDI 測試數據串列輸入

7 TMS 測試模式選擇

9 TCK 測試時鐘

11 RTCK 測試時鐘返回信號

13 TDO 測試數據串列輸出

15 nRESET 目標系統復位信號

17 、 19 NC 未連線

10針

仿真器連線埠 AVR連線埠 備註

1. TCK TCK

2. NC NC

3. TDO TDO

4. Vtref VCC

5. TMS TMS

6. nSRST RESET

7. NC / Vsupply NC / VCC JTAG ICE仿真器:VCC;JTAG ICE mkII仿真器:NC

8. nTRST NC ATMEL尚且保留該連線埠,如今暫不使用它,未來可能會使用

9. TDI TDI

10.GND GND