基本介紹

結構型式,其主要電器特性的典型值如下(不同廠家具體值有差別):

型號 tPd PD

54S373/74S373 7ns 525mW

54LS373/74LS373 17ns 120mW

373 的輸出端 O0~O7 可直接與匯流排相連。

當三態允許控制端 OE 為低電平時,O0~O7 為正常邏輯狀態,可用

74HC373

74HC373 來驅動負載或匯流排。

當 OE 為高電平時,O0~O7 呈高阻態,即不驅動匯流排,也不為匯流排的負載,但

鎖存器內部的邏輯操作不受影響。

當鎖存允許端 LE 為高電平時,O 隨數據 D 而變。當 LE 為低電平時,O 被鎖存在已建立的數據電平。

工作原理

74HC373

74HC373 當 LE 端施密特觸發器的輸入滯後作用,使交流和直流噪聲抗擾度被改善 400mV。 管腳說明:

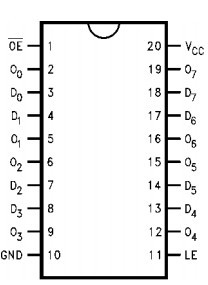

| 1 | OE | 3-state output enable input (active LOW) |

| 2, 5, 6, 9, 12, 15, 16, 19 | Q0 to Q7 | 3-state latch outputs |

| 3, 4, 7, 8, 13, 14, 17, 18 | D0 to D7 | data inputs |

| 10 | GND | ground (0 V) |

| 11 | LE | latch enable input (active HIGH) |

| 20 | VCC | positive supply voltage |

| —— | —— | —— |