簡介

在數字系統中,常要求某些觸發器於同一時刻動作,即同步。為此,引入觸發信號對它們進行控制,使這些觸發器只有在觸發信號變為有效電平後,才能按輸入的置1或置0信號置成相應的狀態。稱這個觸發信號為時鐘信號(Clock) ,記為CLK。要求多個觸發器同時動作時,就用同一個CLK作為同步控制信號。電平觸發RS觸發器也稱同步RS觸發器。由兩部分構成:由與非門G1、G2組成的RS鎖存器和由與非門G3、G4組成的輸入控制電路。為協調各部分的動作,常要求某些觸發器於同一時刻動作。為此,必須引入同步信號,使這些觸發器只有在同步信號到達時才按輸入信號改變狀態。通常把這個同步信號叫做時鐘脈衝,或稱為時鐘信號,簡稱時鐘,用CP(Clock Pulse)表示。同步觸發器又稱為“鍾控觸發器”,即時鐘控制的電平觸發器。電位觸發器具有結構簡單的優點,常用來做鎖存器。動作特點如下:

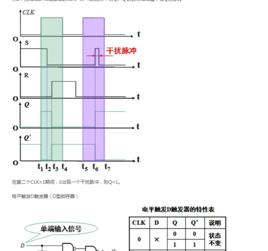

(1)只有當CLK變為有效電平,觸發器才能接受輸入信號,並按照輸入信號將觸發器的輸出置成相應的狀態。(2)在CLK=1的全部時間裡,S和R狀態的變換都可以引起輸入狀態的改變。在CLK回到0以後,觸發器保存的是CLK回到0以前瞬間的狀態。

根據上述的動作特點可以想像到,如果在CLK=1期間S、R的狀態多次改變發生變化,那么觸發器輸出的狀態也將發生多次翻轉,這就降低了觸發器的抗干擾能力。

同步RS觸發器與時鐘信號

在實際的數字系統中往往包含大量的存儲單元,而且經常要求他們在同一時刻同步動作,為達到這個目的,在每個存儲單元電路上引入一個時鐘脈衝(CLK)作為控制信號,只有當CLK到來時電路才被“觸發”而動作,並根據輸入信號改變輸出狀態。把這種在時鐘信號觸發時才能動作的存儲單元電路稱為觸發器,以區別沒有時鐘信號控制的鎖存器。觸發器的電路圖由邏輯門組合而成,其結構均由R-S鎖存器派生而來(廣義的觸發器

電平觸發器

電平觸發器包括鎖存器)。觸發器可以處理輸入、輸出信號和時鐘頻率之間的相互影響。

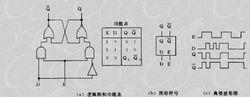

RS觸發器是構成其它各種功能觸發器的基本組成部分。又稱為基本RS觸發器。結構是把兩個與非門或者或非門G1、G2的輸入、輸出端交叉連線。與常規RS觸發器相比,同步RS觸發器多出一個端子,稱為時鐘信號輸入端支結構可以使同步RS觸發器根據時鐘脈衝時序改變輸出狀態。當輸人端(S、R)狀態發生變化.同時只有時鐘信號輸人端有方波信號時,同步RS觸發器狀態才會發生改變。即在時鐘脈衝下降沿時,觸發器才會按照輸入狀態改變輸出狀態,反之亦然 。上升沿觸發器是在時鐘信號由低電平變為高電平(即方波脈衝的上升沿)時根據輸信入號狀態改變輸出狀態,而下降沿觸發器是在時鐘信號由高電平變為低電平(即方波脈衝的下降沿)時根據輸人信號狀態改變輸出狀態,採用邊沿觸發方式可以有效防止觸發電路發生振盪。

時鐘信號是時序邏輯的基礎,它用於決定邏輯單元中的狀態何時更新。時鐘信號是指有固定周期並與運行無關的信號量,時鐘頻率(clock frequency,CF)是時鐘周期的倒數。時鐘邊沿觸發信號意味著所有的狀態變化都發生在時鐘邊沿到來時刻。在邊沿觸發機制中,只有上升沿或下降沿才是有效信號,才能控制邏輯單元狀態量的改變。至於到底是上升沿還是下降沿作為有效觸發信號,則取決於邏輯設計的技術。

同步是時鐘控制系統中的主要制約條件。同步是指在有效信號沿發生時刻,希望寫入單元的數據也有效。數據有效則是指數據量比較穩定(不發生改變),並且只有當輸入發生變化時數值才會發生變化。由於組合電路無法實現反饋,所以只要輸入量不發生變化,輸出最後最終會是一個穩定有效的量。

觸發器

觸發器是能夠存儲一位二值信號的基本單元電路,在外觸發下,兩個穩態可相互轉換。它是構成時序邏輯電路的基本單元電路。觸發器有三個基本特性:有兩個穩態,可分別表示二進制數碼0和1,無外觸發時可維持穩態;外觸發下,兩個穩態可相互轉換(稱翻轉);有兩個互補輸出端。觸發方式有3種:電平觸發、脈衝觸發和邊沿觸發。按照電路結構形式的不同分為:基本SR觸發器、主從觸發器、維持阻塞觸發器、CMOS邊沿觸發器等;按照觸發器邏輯功能的不同分為:SR觸發器、JK觸發器、T觸發器、D觸發器等;按照存儲數據的原理不同分為:靜態觸發器和動態觸發器。