發展背景

神經網路的硬體實現可追溯到60年代,當時有幾家公司和研究機構試圖用硬體來實現神經元,最為著名的便是感知機和ADALINE神經網路模型的實現。當時Comell Aeronautical實驗室(現在名為CALSPAN Corporation)的Rosenblatt從理論上和實現上描述了感知機。ADALINE神經網路模型則是由斯坦福人學的Widrow提出的。感知機和ADALINE均為單個神經元模型,它們均能接受多路輸入,並能自適應地修改與這些輸入相對應的突觸強度(互連權值),然而它們在實現上有所不同。在感知機中,其突觸強度通過一種電子機械的方法來改變(通過一個電動馬達的轉動來改變突觸強度),這種實現有許多缺點,如體積大,價格高,運行不可靠等。Widrow的ADALINE實現中則用電阻的方法來表示突觸強度。

1965年至1980年,除Adaptronics Corp(現為Divisionof Flow General Crop)之外,其它一些研究實體在神經網路實現上沒有做更多的工作。Adaptronics的LouisGilstrap和Roger Barton在1974年開發了第一塊神經元晶片。這種很一般的晶片上只包含一個神經元,具有多個輸入端且其互連強度可以自適應的改變。要構造具有多個神經元的網路,只需將許多這種晶片在外掛程式板上排列並互連起來就可以了。將許多這種外掛程式板構建在一起便可滿足神經網路在商業和軍事上的許多套用目的。1982年美國的物理學家Hopfield發表論文,提出神經網路的一種數學模型,即Hopfield神經網路模型,並研究了它的動力學性質。兩年以後,他設計出了電子線路模擬這種網路的性質,認為這種網路可以解決數學上著名的TSP問題(Traveling Salesman Problem)。次年,美國加州理工學院和貝爾實驗室合作研製成256個神經元(在四分之一平方英寸晶片上,由2.5*10^4個電晶體和1.0"10^5個電阻集成)和64個可程式神經元。

研究意義

在進行神經網路的研究中,要使神經網路在實際中能進行有效的套用,或是支持更好的神經網路研究,神經網路實現技術必須能夠支持大規模的神經網路模型的神經計算,同時要能儘可能地縮短神經計算的時間j達到實時的水平。但是現有的各種神經網路軟體模擬環境所能支持模擬神經網路模型的規模及神經計算速度都還遠遠達不到研究和套用所需要的水平。因此,開展大規模的硬體實現的神經網路計算機的研製勢在必行。

硬體實現技術

神經網路的實現技術可以分為硬體實現和虛擬實現兩個方面。所謂硬體實現是指物理上的處理單元及處理單元之間通訊與一個具體問題的神經網路模型中的神經元及連結一一對應,每一神經元及每一連線都有與之對應的物理器件。全硬體實現的最大優點是處理速度快,且易於滿足實時性要求,但是缺乏通用性、靈活性和可程式性。硬體實現研究的核心是神經器件的構造。當前國際上該項目研究的主要內容有:

1)電子神經晶片的研究;

2)光學神經晶片的研究;

3)分子/生物神經晶片的研究;

硬體實現方法

當前神經網路的套用實現方法主要還停留在用現有的Von.Neumann體系計算機模擬實現神經網路。這種做法的明顯缺點就是,現有的計算體系不適合神經網路的結構特點。在某些實時控制的套用場合,這樣的系統無論從體積還是速度方面都無法滿足實用的需要。因此,在這種套用場合下,用新的硬體技術直接實現神經網路的要求就更加迫切了。

神經網路的硬體實現方法可分為以下幾種:

1.超大規模積體電路(VLSI,Very Large Scale Integrated Circuit)處理器:又可分為模擬VLSI實現、數字VLSI實現、模/數混合VLSI實現和光電實現;

2.光處理器:分為純光學處理器和光電混合處理器;

3.分子處理器:有磁性材料處理器和生物材料處理器;

4.量子處理器。

主要實現硬體

研究人員提出了多種神經網路專用硬體實現的方法和技術,包括FPGA實現、神經晶片以及DSP加速板等.

FPGA

FPGA是英文Field Programmable Gate Array的縮寫,即現場可程式門陣列,它是在PAL、GAL、EPLD等可程式器件的基礎上進一步發展的產物。它是作為專用積體電路(ASIC)領域中的一種半定製電路而出現的,既解決了定製電路的不足,又克服了原有可程式器件門電路數有限的缺點。

簡單地說,FPGA是一個具有大量通用邏輯單元的器件,而且這些邏輯單元之間有通用的連線。通過把程式下載到FPGA晶片里,這些邏輯單元之間的連線方式被相應改變,從而使FPGA實現相應的功能。基於FPGA的可重新配置的計算結構非常適合於實現神經網路,具有非常多的優點。

神經網路硬體

神經網路硬體超大規模積體電路VLSI

近年來,隨著工藝的進步,數字VLSI成為了神經網路硬體實現的主要方法.其突出優點在於器件性能穩定、數據存儲方便、設計工具豐富、開發周期較短等.儘管有諸多優點,神經網路數字VLSI的實現仍面臨著硬體靈活性較差的問題.因為神經網路是與套用密切相關的,不同套用對象(例如不同的控制對象)所採用的神經網路在規模結構、傳遞函式甚至學習算法上都有所差別,而硬體設計一旦確定,其更改變化將比較困難。

神經網路硬體

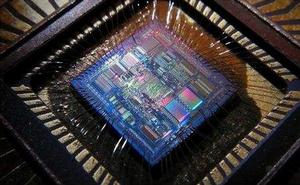

神經網路硬體神經晶片

從1993年起就有一類神經型態晶片可供使用了。1993年一個小獨立團隊帶著一個想法來到了IBM,這個團隊想研發一款神經網路晶片,他們把它稱為ZISC(零指令型計算機),這款晶片成為世界上第一個商用神經型態晶片。

神經晶片是一個帶有多個處理器、讀寫/唯讀存儲器(RAM和ROM)以及通信和I/O接口的單晶片系統。唯讀存儲器包含一個作業系統、LonTalk協定和I/O功能庫。晶片有用於配置數據和應用程式編程的非易失性存儲器,並且兩者都可以通過網路下載。