介紹

浮點乘法器是現代微處理器的重要協處理器部件,是實時圖像處理和數位訊號處理的核心,因此人們對提高浮點乘法器的性能進行了大量的研究。一般來說,浮點乘法包括符號位異或、指數相加和尾數相乘三部分。其中,符號位和指數位運算相對簡單,尾數相乘部分則比較複雜,涉及多個部分積的產生及累加,以及累加結果的捨入。因此,提高浮點乘法器的性能主要是針對尾數相乘部分的。

浮點標準

浮點乘法器是現代微處理器的重要組成部件,由IEEE定義的IEEE 754浮點標準是目前廣泛被採用的一個標準。IEEE 754定義了4種浮點數格式:單精度、擴展單精度、雙精度和擴展雙精度,其中使用最廣的是單精度浮點格式。

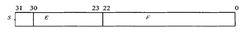

IEEE 754單精度浮點數格式為32位,如圖1所示,其中偏移值為127,尾數有一位隱藏位。

浮點乘法器

浮點乘法器圖1

第31位是符號位(S),第30至23位是8位的階碼(E),第22至0位是23位的尾數(F)。特殊數操作規則如下:

浮點乘法器

浮點乘法器表1

結構

浮點乘法器是現代微處理器的重要協處理器部件,是實時圖像處理和數位訊號處理的核心,因此人們對提高浮點乘法器的性能進行了大量的研究。

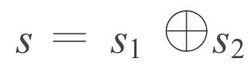

如圖2所示,一般來說,浮點乘法包括符號位異或、指數相加和尾數相乘三部分。其中,符號位和指數位運算相對簡單,尾數相乘部分則比較複雜,涉及多個部分積的產生及累加,以及累加結果的捨入。因此,提高浮點乘法器的性能主要是針對尾數相乘部分的。現行的浮點乘法器大多採用圖2中的結構,由於尾數在捨入過程中可能溢出,捨入後還需要規格化,因此捨入邏輯需要兩個規格化過程(即捨入前規格化和捨入後規格化),比較複雜。另外,現行浮點乘法器大多採用單一捨入模式(RN模式),不能和IEEE 754標準完全兼容。針對浮點乘法器傳統捨入方法的這些不足,我們套用快速捨入思想構建了一種基於預測和選擇的快速捨入方法,以提高浮點乘法器的性能 。

浮點乘法器

浮點乘法器圖2

快速捨入是提前算出各種可能的尾數值,然後根據捨入模式和捨入信息選擇出正確的尾數值。它由三部分構成:

(1)捨入表構建;

(2)預測方案構建;

(3)尾數值選擇。

捨入表列出了可能的尾數值,預測可以減少這些尾數值,尾數值選擇則可以大大地簡化捨入邏輯。

實現

頂層設計

浮點乘法器首先要對輸入的兩個運算元進行判斷,若為非規格化數,則按表1所列的規則進行處理,若為規格化數則要進行如下的預處理:

浮點乘法器

浮點乘法器 浮點乘法器

浮點乘法器 浮點乘法器

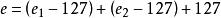

浮點乘法器(1)求兩個運算元的階碼之和:設這兩個運算元的階碼分別為 、 ,則得到臨時的階碼 。e只是臨時的階碼,因為最後對乘積所得到的尾數進行規格化後,可能還要修改階碼。

浮點乘法器

浮點乘法器 浮點乘法器

浮點乘法器(2)求兩運算元相乘後的符號:設這兩個運算元的符號分別為 、 ,則相乘後的符號位為

浮點乘法器

浮點乘法器 浮點乘法器

浮點乘法器 浮點乘法器

浮點乘法器(3)修改兩運算元的尾數。設這兩個運算元的符號分別為 、 。則:

浮點乘法器

浮點乘法器 浮點乘法器

浮點乘法器 浮點乘法器

浮點乘法器 浮點乘法器

浮點乘法器 浮點乘法器

浮點乘法器 浮點乘法器

浮點乘法器修改後 =‘1’& ,即 從原來的23位變位24位;修改後 =‘1’& ,即 從原來的23位變位24位。

預處理結束後將進行尾數的乘法運算。由前面可知這時尾數己是24位,所以進行乘法運算的將是一個24位的乘法器。這個乘法器是整個器件的核心部件,它將直接影響浮點乘法器的處理速度。

最後將所得的尾數進行規格化和捨入。兩個24位的尾數相乘將得到一個48位(47~0)的尾數,輸出時只取第46至第24位。

規格化:當尾數的最高位為0,將尾數左移1位;當尾數的最高位為1,則尾數不變,將前面所求的臨時的階碼加1。

捨入:當尾數的第23位為0,捨去(23—0);當尾數的第23位為1,向第24位進1並捨去(23—0)。

流程如圖3所示:

浮點乘法器

浮點乘法器圖3

基本算法乘法器的設計實現

乘法器的基本算法:

(1)定義一個24位的臨時的尾數temp-mart,和一位的進位位C;

(2)判斷乘數(mantB)的低位是否為1,是則將temp-mant和被乘數(mantA)相加,若有進位則將C置1,否則temp-mant不變;

(3)將C、temp-mant、mantB聯合右移一位;

(4)判斷manta的所有位是否檢查完,若沒有則重複(2)(3),直至檢查完輸出結果。

陣列算法乘法器的設計實現

從以上基本算法乘法器的實現,可以看出它實際上是一個疊代的過程,疊代的次數和乘數位相同。由於疊代的操作是對“部分積”進行累加,可以暫時分別保存每位的進位,等到下一次一起相加。所以陣列算法乘法器的核心是要構造一個進位保存加法器(CSA) 。

乘法器的陣列算法:

(1)乘數B的最低位即B(0)和被乘數A (24位),輸入進位位X“000000”(24位),輸入給進位保存加法器(CSA),輸出為積S(0)(24位),和輸出進位位C(24位)。將輸出的積S的最低位作為最終結果的最低位P(0)。並將輸出的積S右移一位最高位補0,作為臨時積tempS(0)的值。

(2)B的下一位B(i)和被乘數A(24位),輸入進位位為前一次的輸出進位位C(i—1)輸入給進位保存加法器(CSA),輸出為積S(i)和輸出進位位C(i)。將輸出的積S(i)的最低位作為最終結果的第i位P(i),並將輸出的積S(i)右移一位最高位補0,作為臨時積temps (i)的值。

(3)乘數B的所有位是否都檢查完了,否則重複(2),若是則進入(4)。

(4)將temps(23)、C(23)和一位的進位位‘0’,輸入給一個普通的24位加法器,輸出給最終結果的高24位。

Booth乘法器的實現

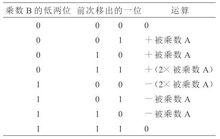

從上面的陣列乘法器的實現中可以發現,它只是檢查乘數的一位二進制位。下面根據Booth 4基乘法算法(見表2),實現一次檢查乘數兩位二進制位的乘法器。

Booth乘法器的算法:

將乘數B的低兩位和前一次移出的一位,以及被乘數A和“部分積”輸入給Booth算法單元,直至乘數B的所有位都檢查完.所以Booth乘法器的核心時Booth算法單元,它將根據表2求出部分積 。

浮點乘法器

浮點乘法器表2