簡介

欠壓鎖定(Undervoltage-Lockout)簡稱 UVLO,是電子設備中在電源電壓低於正常工程準位時,切斷電源的電路。在嵌入式系統中常會用UVLO監控電池電壓,若電壓低於一定值,會直接切斷電源,保護嵌入式系統的電路。

許多電子設備中都有UVLO的功能,例如在鎮流器中就有UVLO電路,若電壓過低時直接切斷電源。

UVLO就是低電壓鎖定; 低壓關斷. 欠壓關斷模式是當供電電壓低於IC的開啟門限電壓時的一種保護模式。欠壓關斷模式可保證IC在供電電壓不足時不致於被損壞。一個低電壓鎖定(UVLO)電路可確保IC在電池電壓未達到安全操作電壓前不會激活,UVLO的功能會展示滯後現象,以確保在電源供應上的噪音不會不慎導致系統故障。

UVLO的遲滯功能是防止電壓在UVLO那一點的時候,出現振盪,所以加個遲滯.

為了更穩定的工作,某些 DC/DC 轉換器具有 UVLO(欠壓鎖定)功能。電源開啟後,UVLO 功能使內部電路處於待機狀態,直到DC/DC 轉換器的輸入電壓(VIN)達到 UVLO 電壓,以此來減少消費電流並避免誤操作。

欠壓鎖定電路

在DC-DC電源管理晶片中,電壓的穩定尤為重要,因此需要在晶片內部集成欠壓鎖定電路來提高電源的可靠性和安全性。對於其它的積體電路,為提高電路的可靠性和穩定性,欠壓鎖定電路同樣十分重要。

傳統的欠壓鎖定電路要求簡單、實用,但忽略了欠壓鎖定電路的功耗,使系統在正常工作時,仍然有較大的靜態功耗,這樣就降低了電源的效率,並且無效的功耗增加了晶片散熱系統的負擔,影響系統的穩定性。

基於傳統的欠壓鎖定電路,本文提出一種CMOS工藝下的低壓低靜態功耗欠壓鎖定電路,並通過HSPICE仿真。此電路可以在1.5V~6V的電源電壓範圍下工作,閾值可調,翻轉速度很快。電源電壓正常工作時,此電路的靜態功耗可低於2μW。此電路結構簡單,用標準CMOS工藝實現容易,可用於由電池供電的電源管理晶片或便攜設備中作欠壓保護電路。

欠壓鎖定電路工作原理

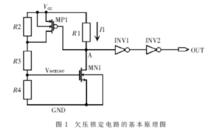

圖1.欠壓鎖定電路

圖1.欠壓鎖定電路欠壓鎖定電路的基本原理圖如圖1所示。電路包括電壓採樣電路、比較器、輸出緩衝器和反饋迴路。Vcc為待檢測的電源電壓,電阻R2、R3、R4組成Vcc的分壓採樣電路,實現對Vcc的採樣;NMOS開關管MNl和電阻R1構成比較器,對採樣電壓和MNl的VTH進行比較,並輸出比較結果;反向器INV1和INV2組成緩衝器電路,可對比較器的輸出波形進行整形和緩衝,提高電路的負載能力;PMOS開關管MP1構成正反饋迴路,可以實現電路的遲滯功能,防止電路在Vcc的閾值附近振盪,增加系統的穩定性。調整R2、R3、R4的大小可實現不同閾值和遲滯量的Vcc欠壓保護。