百科名片

基於CMOS工藝的高性能處理器時鐘系統,集成PLL可以從內部觸發,比從外部觸發更快且更準確,能有效地避免一些與信號完整性相關的問題。

本文介紹了一種基於CMOS工藝的高性能處理器時鐘系統設計,設計頻率為200MHz,VCO的相位噪聲為-110dBC/Hz@100kHz。作者詳細分析了鎖相環路的結構及組成,並介紹了消除噪聲的設計方法。VSPACE=12 HSPACE=12 ALT="圖1:鎖相環在時鐘產生中套用。

鎖相環廣泛套用於時鐘系統設計中,其中包括相位同步以及時鐘倍頻等套用。通常,當晶片工作頻率高於一定頻率時,就需要消除由於晶片內時鐘驅動所引起的片內時鐘與片外時鐘間的相位差,嵌入在晶片內部的PLL可以消除這種時鐘延時。此外,很多晶片控制鏈邏輯需要占空比為50%的時鐘,因此需要一個2倍於此的時鐘源,集成在晶片內部的PLL可以將外部時鐘合成為此時鐘源。

系統集成 PLL可以從內部觸發,比從外部觸發更快且更準確,能有效地避免一些與信號完整性相關的問題。系統集成PLL的另一個顯著特點是通過調節位於鎖相環反饋迴路中的時鐘樹緩衝區中的參數,鎖相環能夠產生相對於參考輸入時鐘頻率不同倍率的核心時鐘,這種調節能確保晶片和外部接口電路之間快速同步和有效的數據傳輸。

在高性能處理器時鐘系統設計中,通常需要鎖相環產生片上時鐘。本文以一種200MHz的時鐘系統設計為實例介紹一種基於鎖相環的時鐘系統設計,其中輸入參考頻率是25MHz,相位噪聲為-100dBc/Hz@100kHz,壓控振盪器增益為380MHz/V,工作電壓為5V。仿真和測試結果表明該設計能滿足系統要求。

環路結構

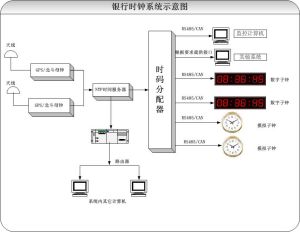

以鎖相環為基礎的時鐘產生結構如圖1所示:外部25MHz的參考時鐘信號或匯流排時鐘(BusCLK)先進入到一個接收緩衝器,在進入鑒頻鑒相器(PFD)之前要經過一個分頻器,分頻係數為M1,得到圖1中φi,然後與從分頻器M6來的內部反饋信號Фo在PFD中比較,得到誤差信號Фe,它將作為電荷泵以及濾波網路的輸入,用以控制壓控振盪器(VCO)。VSPACE=12 HSPACE=12 ALT="圖2:鑒相器結構。

VCO的輸出先經過M3分頻,再通過緩衝以後產生系統的主時鐘PClk。同時,主時鐘在進入分頻器M6之前先通過H樹形時鐘分布網路,最後返回鑒相器,這樣就形成了整個反饋迴路。從平衡的角度來看, PFD的兩個輸入必須在頻率和相位上保持一致,因此所得到的晶片核心時鐘和輸入的匯流排時鐘的比值fpclk/fbus必須與M6/M1相等。通過改變M6以及M1的值,可以得到輸入時鐘頻率的整數倍或者分數倍值。由於晶片要求時鐘不能出現漂移,所以輸出時鐘占空比以及系統的相位調整能力必須對環境以及工藝參數變化不敏感。VCO的輸出也可以切換到分頻器M5上,得到的輸出可作為二級高速快取(L2)的時鐘。同理,fvco=M3×fpclk =M5×fL2CLK,二級快取的輸出頻率也可以通過調整M3以及M1來得到理想的值。

環路構成

整個環路中包括鑒相器、濾波器、壓控振盪器、分頻器、共模抑制和鎖定檢測等模組,以下介紹主要模組的結構:

1. 鑒相器VSPACE=12 HSPACE=12 ALT="圖3:壓控振盪器結構。

數字鑒頻鑒相器產生的輸出信號能夠表達頻率及相位相對超前或者滯後信息,然後送到電荷泵。復位信號到達以後,θi的每一個上升沿都觸發“UP”信號,直到θo的一個上升沿到達,這樣就結束UP的置位狀態轉入系統復位狀態。同樣,如果θo上升沿先於θi到達, “DOWN”被置位,直到θi的一個上升沿到達,繼而轉入復位狀態。除非兩個輸入相位以及頻率非常接近,即進入所謂的“鑒相死區”,一般脈衝的寬度正比於兩個輸入之間的相差大小。鑒相器結構如圖2所示。

2. 壓控振盪器

壓控振盪器是鎖相環中關鍵部件,在實際套用中有很多種結構,圖3是一種常用的結構。其中D延遲單元是整個環路的關鍵部件,選擇單元M負責選擇不同的數據通道。

從圖3中可以看出,整個壓控振盪器是建立在一個帶有內部延遲單元的環形振盪器基礎上。與灌電流型以及電流調製型壓控振盪器相比較,此類差分環形振盪器非常廣泛地用在晶片時鐘發生電路中,同時內嵌延時單元的壓控振盪器有相對較低的VCO增益,所以非常適合於差分控制以及信號路徑上電路的實現。實驗表明,具有低增益內嵌延時單元的振盪器的“抖動”明顯比高增益環小很多,因為在低增益結構中噪聲很容易解耦。振盪器內嵌延遲環節的工作頻率一般有一定限制,為確保環路單調性,一般上下限之比必須小於2:1,但也可以通過選擇適當的分頻器比例係數,或者在VCO的信號路徑上增加編程能力來有效提高其工作頻率範圍。VSPACE=12 HSPACE=12 ALT="圖4:VCO的噪聲曲線。

壓控振盪器的頻率範圍取決於路徑上最長、最短延時,如圖3所示,外圍虛線框表示最大頻率fh的路由,它歷經3個延時單元D以及一個選擇單元M,內虛線框表示最小頻率fl的路由,它的路徑包括6個延時單元D以及一個選擇單元M,不同單元的選擇同時會影響壓控振盪器的增益以及環路中心頻率。頻率範圍可以用多路開關來選擇不同延時路徑來單獨確定,從而非常靈活地調節VCO的頻率範圍,遠超於由VCO增益所決定的頻率範圍。

延遲單元及選擇單元可以建立在PMOS型源耦合差分放大器基礎上,該類型放大器帶有NMOS型負載,它同時能實現壓控擺幅調整,主要通過調整電壓及改變有效負載線來實現。電流源的高阻態增加了對源耦合部件的電源噪聲抑制,同時,N阱也有效地隔離了P型襯底上的大量噪聲,增加系統噪音抑制性能。

仿真結果

使用Cadence中的SpectreRF對所設計電路進行仿真,利用0.6μm,3V/5V,雙多晶(Double Poly)、雙鋁(Double Metal)CMOS工藝參數。VCO是鎖相環中關鍵模組,對VCO做PSS以及PNoise分析,可得到其相位噪聲圖形,如圖4所示,在100kHz處相位噪聲近似為-110dBc/Hz。圖5是VCO的增益曲線,增益約為380MHz/V,有較好的線性度。

設計總結

由於鎖相環中包含模擬電路,噪聲干擾也是設計中需要克服的問題。大型數字電路翻轉所產生的電源噪聲影響鎖相環中模擬電路的工作,輸出的時鐘周期將會因為電源噪聲或者其它干擾源(例如MOS管的熱噪聲)的影響而改變,通常把它稱為輸出“抖動”。時鐘抖動將直接影響到積體電路最高的運行頻率,因為它將減少可用的時鐘周期。隨著可用時鐘周期減少,在關鍵路徑上的數字電路在一個周期內得不到足夠長的時間來處理數據,直接導致所謂 “關鍵路徑錯誤”。此外,有大功率晶片干擾或者數模混合電路共襯底時,電源噪聲的影響更加明顯。VSPACE=12 HSPACE=12 ALT="圖5:VCO的增益曲線。

頻率為fm的噪聲源在輸出端引起的頻率偏差Δfout以及相位偏差Δθout可以表示為

Δθout=Δ

高頻噪聲和低頻噪聲因產生機理不同而體現出來的性能也相差很大,所以在不同的套用場合對其採取的抑制方式也不一樣。低頻噪聲一般包括電源紋波、電阻和電晶體隨機熱噪聲、電晶體隨機閃變噪聲等。高頻噪聲主要是來自數字電路的高速翻轉以及晶片控制部件的快速切換,在晶片時鐘設計中,該類型噪聲占主導地位。高頻噪聲因為其頻率比較高,所產生的相位偏移Δθout比較小,一般高頻噪聲用周期性的“抖動”來描述。

經典的鎖相環路中包含有模擬電路,因此對噪聲非常敏感,對於片上集成的鎖相環路一般採用以下措施來消除噪聲:

1. 用電源和地線包圍整個鎖相環。地線圈能夠使鎖相環周圍的襯底電位保持穩定,恆定的襯底電位能夠抑制噪聲,而輸入輸出單元以及其它邏輯電路引入的噪聲大部分是通過襯底耦合引入的。

2. 將鎖相環路的電源線與晶片其它系統的電源線分離。因為經常在邏輯電路部分或者接口電路部分出現瞬間大電流,導致主電源的電位不斷變化。電源電壓不斷變化將影響鎖相環噪聲抑制功能,所以在設計鎖相環路的電源以及地時,應該考慮將主電源部分與鎖相環電源部分分離,並且都用單獨的引腳給出。

3. 把鎖相環路的輸入引腳放置在鎖相環路旁邊,以免其受到電源波動以及其它干擾的影響。