基本功能

或非門

或非門或非門是具有多端輸入和單端輸出的門電路。當任一輸入端(或多端)為高電平(邏輯“1”)時,輸出就是低電平(邏輯“0”);只有當所有輸入端都是低電平(邏輯“0”)時,輸出才是高電平(邏輯“1”) 。其邏輯關係的數學表達式為: ,其二輸入的或非門真值表如下表所示。

| 輸入A | 輸入B | 輸出Y |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

邏輯符號

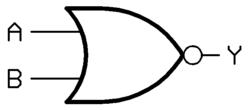

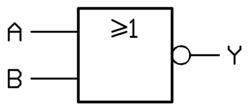

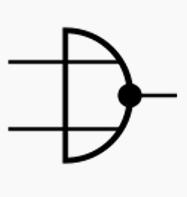

或非門有3種邏輯符號,包括:形狀特徵型符號(ANSI/IEEEStd 91-1984)、IEC矩形國標符號(IEC 60617-12)和DIN符號(DIN 40700),以二輸入或門為例,邏輯符號如圖所示:

ANSI/IEEE Std 91-1984 ANSI/IEEE Std 91-1984 |  IEC 60617-12 IEC 60617-12 |  DIN 40700 DIN 40700 |

實現

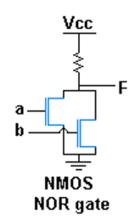

NMOS邏輯實現

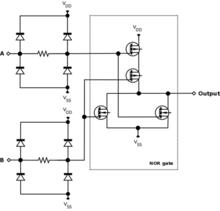

NMOS邏輯

NMOS邏輯上圖展示了使用NMOS線路的2輸入或非門的構造。如果輸入都是高電平,對應的NMOS就會接通,輸出會被拉到低電平;反之輸出會通過上拉電阻被拉到高電平。

CMOS邏輯實現

無緩衝CMOS 2輸入或非門

無緩衝CMOS 2輸入或非門上圖展示了使用CMOS技術的2輸入或非門。輸出端的二極體和電阻用來保護CMOS元件,以防其受到靜電放電(ESD)的損害,從而在電路的邏輯功能中發揮不了作用。

其他方案

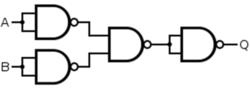

在絕大多數但不是所有的電路設計中,邏輯非的功能本身就包含在結構中,如CMOS和TTL等。在這樣的邏輯系列中,要實現或門,唯一的方法是用2個或更多的邏輯門來實現,如一個或非門加一個反相器。具體方法是將兩個輸入接在一起的與非門作為另外一個與非門的兩個輸入,然後在後者的輸出接一個輸入接在一起的與非門,即可實現或非門。注意任何邏輯門都可以用與非門的組合或或非門的組合實現。

通過與非門構建的或非門 通過與非門構建的或非門 |

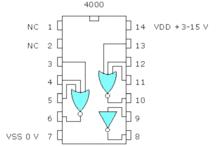

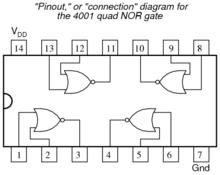

積體電路

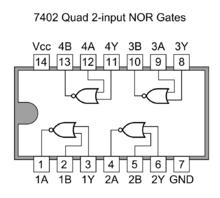

或非門是基本的邏輯門,因此在TTL和CMOS積體電路中都有標準邏輯晶片。標準的4000系列CMOS積體電路有:CD4000,包含兩個3輸入端或非門和一個單非門;CD4001,包含四個2輸入端或非門;CD4002,包含兩個4輸入端或非門。 標準的74系列積體電路有:74X02,包含四個2輸入端或非門;74X27,包含三個3輸入端或非門;7428,包含兩個4輸入端或非門。引腳分配如下:

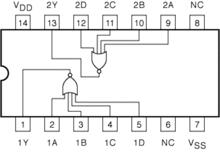

CD4000 CD4000 |  CD4001 CD4001 |  CD4002 CD4002 |

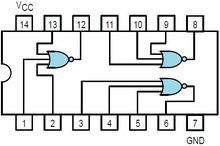

74X27 74X27 |  74X02 74X02 |