套用舉例

真值表

一位全加器的真值表如下圖,其中Ai為被加數,Bi為加數,相鄰低位來的進位數為Ci-1,輸出本位和為Si。向相鄰高位進位數為Ci

| 輸入 | 輸出 | |||

| Ci-1 | Ai | Bi | Si | Ci |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

描述

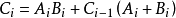

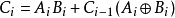

一位全加器的表達式如下:

S=A⊕B⊕C

全加器

全加器第二個表達式也可用一個異或門來代替或門對其中兩個輸入信號進行求和:

全加器

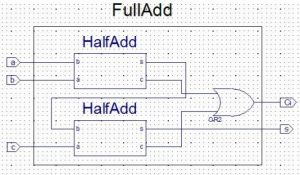

全加器硬體描述語言Verilog 對一位全加器的三種建模方法:

結構化描述方式

全加器

全加器moduleFA_struct(A,B,Cin,Sum,Count);

inputA;

inputB;

inputCin;

outputSum;

outputCount;

wireS1,T1,T2,T3;

//--statements--//

xorx1(S1,A,B);

xorx2(Sum,S1,Cin);

andA1(T3,A,B);

andA2(T2,B,Cin);

andA3(T1,A,Cin);

orO1(Count,T1,T2,T3);

endmodule

該實例顯示了一個全加器由兩個異或門、三個與門、一個或門構成。S1、T1、T2、T3則是門與門之間的連線。代碼顯示了用純結構的建模方式,其中xor、and、or是VerilogHDL內置的門器件。以xorx1(S1,A,B)該例化語句為例:xor表明調用一個內置的異或門,器件名稱xor,代碼實例化名x1(類似原理圖輸入方式)。括弧內的S1,A,B表明該器件管腳的實際連線線(信號)的名稱,其中A、B是輸入,S1是輸出。

數據流描述方式

`timescale 1ns/100ps

module FA_flow(A,B,Cin,Sum,Count);

input A,B,Cin;

output Sum, Count;

wire S1,T1,T2,T3;

assign # 2 S1 = A ^ B;

assign # 2 Sum = S1 ^ Cin;

assign #2 T3 = A & B;

assign #2 T1 = A & Cin;

assign #2 T2 = B & Cin ;

assign #2 Count=T1 | T2 | T3;

endmodule

注意在各assign 語句之間,是並行執行的,即各語句的執行與語句之間的順序無關。如上,當A有個變化時,S1、T3、T1 將同時變化,S1的變化又會造成Sum的變化。

3.)行為描述方式:

module FA_behav(A, B, Cin, Sum, Cout );

input A,B,Cin;

output Sum,Cout;

reg Sum, Cout;

reg T1,T2,T3;

always@ ( A or B or Cin )

begin

Sum = (A ^ B) ^ Cin ;

T1 = A & Cin;

T2 = B & Cin ;

T3 = A & B;

Cout = (T1| T2) | T3;

end

endmodule

全加器的VHDL描述

library ieee;

use ieee.std_logic_1164.all;

Entity full_add is

port(a,b,c:in std_logic;

sum,count:out std_logic);

end entity full_add;

architecture art of full_add is

begin

process(a,b,c) is

begin

if(a="0" and b="0" and c="0") then

sum<="0";count<="0";

elsif(a="1" and b ="0" and c="0") then

sum<="1";count<="0";

elsif(a="0" and b="1" and c= '0') then

sum<="1";count<="0";

elsif(a="1" and b="1" and c= '0') then

sum<="0";count<="1";

elsif(a="0" and b="0" and c= '1') then

sum<="1";count<="0";

elsif(a="1" and b="0" and c= '1') then

sum<="0";count<="1";

elsif(a="0" and b="1" and c= '1') then

sum<="1";count<="0";

else

sum<="1";count<="1";

end if;

end process;

end architecture art;