結構介紹

並行體系結構出現主要因為隨著各個領域對高性能計算的要求越來越高,尤其是多媒體領域大數據量高實時性的需求,使得傳統的單處理器體系結構已經很難適應大規模並行計算的需求,於是多處理器並行體系結構逐漸成為研究的熱點。

多種級別的並行度現在已經成為計算機設計的推動力量,而能耗和成本則是主要約束條件。應用程式中主要有以下兩種並行。

(1) 數據級並行(DLP),它的出現是因為可以同時操作許多數據項。

(2) 任務級並行(TLP),它的出現是因為創建了一些能夠單獨處理但大量採用並行方式執行的工作任務。

計算機硬體又以如下4種主要方式來開發這兩種類型的套用並行。

(1) 指令級並行在編譯器的幫助下,利用流水線之類的思想適度開發數據級並行,利用推理執行之類的思想以中等水平開發數據級並行。

(2) 向量體系結構和圖形處理器(GPU)將單條指令並行套用於一個數據集,以開發數據級並行。

(3) 執行緒級並行在一種緊耦合硬體模型中開發數據級並行或任務級並行,這種模型允許在並行執行緒之間進行互動。

(4) 請求級並行在程式設計師或作業系統指定的大量去耦合任務之間開發並行。

並行體系結構有以下五種訪存模型:均勻訪存模型(UMA)、非均勻訪存模型(NUMA)、全高速快取訪存模型(COMA)、一致性高速快取非均勻存儲訪問模型(CC-NUMA)和非遠程存儲訪問模型(NORMA)。

並行性

同時性:兩個或兩個以上的事件在同一時刻發生。

並發性:兩個或兩個以上的事件在同一時間間隔發生。

分類

⑴從處理數據的角度看,並行性等級從低到高可分為四類。

字串位串

同時只對一個字的一位進行處理。這是最基本的串列處理方式,不存在並行性。

字串位並

同時對一個字的全部位進行處理,不同字之間是串列的。這裡已開始出現並行性。

字並位串

同時對許多字的同一位進行處理。這種方式有較高的並行性。

全並行

同時對許多字的全部位進行處理。這是最高一級的並行。

⑵從執行程式的角度看,並行性等級從低到高也可分為四類。

指令內部並行

一條指令執行時各微操作之間的並行。

指令級並行

並行執行兩條或多條指令。

任務級或過程級並行

並行執行兩個以上過程或任務(程式段)。

作業或程式級並行

並行執行兩個以上作業或程式。

分類法

Flynn分類法

1966年,Michael J.Flynn提出根據指令流、數據流的並行度對計算機系統進行分類,定義如下。

·指令流:機器執行的指令序列

·數據流:由指令流調用的數據序列,包括輸入數據和中間結果

·並行度:指令或數據並行執行的最大可能數目。

Flynn根據不同的指令流-數據流組織方式把計算機系統分為4類。

1·單指令流單數據流(Single Instruction Stream Single DataStream,SISD)

SISD其實就是傳統的順序執行的單處理器計算機,其指令部件每次只對一條指令進行解碼,並只對一個操作部件分配數據。

2·單指令流多數據流(Single Instruction Stream Multiple Data Stream,SIMD)

SIMD以並行處理機為代表,結構如圖,並行處理機包括多個重複的處理單元PU1~PUn,由單一指令部件控制,按照同一指令流的要求為它們分配各自所需的不同的數據。

3·多指令流單數據流(Multiple Instruction Stream Single Data Stream,MISD)

MISD的結構,它具有n個處理單元,按n條不同指令的要求對同一數據流及其中間結果進行不同的處理。一個處理單元的輸出又作為另一個處理單元的輸入。

4·多指令流多數據流(Multiple Instruction Stream Multiple Data Stream,MIMD)

MIMD的結構是指能實現作業、任務、指令等各級全面並行的多機系統,多處理機就屬於MIMD。

馮式分類法

1972年馮澤雲提出用最大並行度來對計算機體系結構進行分類。所謂最大並行度Pm是指計算機系統在單位時間內能夠處理的最大的二進制位數。設每一個時鐘周期△ti內能處理的二進制位數為Pi,則T個時鐘周期內平均並行度為Pa=(∑Pi)/T(其中i為1,2,…,T)。平均並行度取決於系統的運行程度,與應用程式無關,所以,系統在周期T內的平均利用率為μ=Pa/Pm=(∑Pi)/(T*Pm)。用平面直角坐標系中的一點表示一個計算機系統,橫坐標表示字寬(N位),即在一個字中同時處理的二進制位數;縱坐標表示位片寬度(M位),即在一個位片中能同時處理的字數,則最大並行度Pm=N*M。

由此得出四種不同的計算機結構:

①字串列、位串列(簡稱WSBS)。其中N=1,M=1。

②字並行、位串列(簡稱WPBS)。其中N=1,M>1。

③字串列、位並行(簡稱WSBP)。其中N>1,M=1。

④字並行、位並行(簡稱WPBP)。其中N>1,M>1。

MIMD分類

並行向量

向量處理器,又稱數組處理器,是的一種實現了直接操作一維數組(向量)指令集的中央處理器(CPU)。這與一次只能處理一個數據的標量處理器正相反。向量處理器可以在特定工作環境中極大地提升性能,尤其是在數值模擬或者相似領域。向量處理器最早出現於20世紀70年代早期,並在70年代到90年代期間成為超級計算機設計的主導方向,尤其是多個克雷(Cray)平台。由於常規處理器設計性價比的快速下降,基於向量處理器的超級計算機在90年代末逐漸讓出了主導地位。

現在,絕大多數商業化的CPU實現都能夠提供某種形式的向量處理的指令,用來處理多個(向量化的)數據集,也就是所謂的SIMD(單一指令、多重數據)。常見的例子有VIS,MMX,SSE,AltiVec和AVX。向量處理技術也能在遊戲主機硬體和圖形加速硬體上看到。在2000年,IBM,東芝和索尼合作開發了Cell處理器,集成了一個標量處理器和八個向量處理器,套用在索尼的PlayStation 3遊戲機和其他一些產品中。

對稱多重

對稱多處理(英語:Symmetric multiprocessing,縮寫為 SMP),也譯為 均衡多處理、 對稱性多重處理,是一種多處理器的電腦硬體架構,在對稱多處理架構下,每個處理器的地位都是平等的,對資源的使用許可權相同。現代多數的多處理器系統,都採用對稱多處理架構,也被稱為對稱多處理系統(Symmetric multiprocessing system)。在這個系統中,擁有超過一個以上的處理器,這些處理器都連線到同一個共享的主存上,並由單一作業系統來控制。在多核心處理器的例子中,對稱多處理架構,將每一個核心都當成是獨立的處理器。

在對稱多處理系統上,在作業系統的支持下,無論進程是處於用戶空間,或是核心空間,都可以分配到任何一個處理器上運行。因此,進程可以在不同的處理器間移動,達到負載平衡,使系統的效率提升。

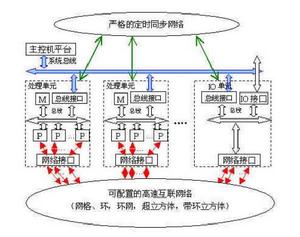

大規模並行

大規模並行處理機(Massively Parallel Processor)是由多個由微處理器,局部存儲器及網路接口電路構成的節點組成的並行計算體系;節點間以定製的高速網路互聯。大規模並行處理機是一種異步的多指令流多數據流,因為它的程式有多個進程,它們分布在各個微處理器上,每個進程有自己獨立的地址空間,進程之間以訊息傳遞進行相互通信。