簡介

JITTER

JITTER所謂jitter就是一種抖動。具體如何解釋呢?其定義延遲從來源地址將要傳送到目標地址,會發生不一樣的延遲,這樣的延遲變動是jitter讓我們來看一個例子。假如你有個女友,你希望她每天晚上下班之後7點來找你,

而有的時候她6:30到,有的時候是7:23,有的時候也許是下一天。這種時間上的不穩定就是jitter。如果你多觀察這種時間上的不規律性,你會對jitter有更深一些的理解。在你觀察的這段期間內,女友最早和最晚到來的時間被稱為“jitter全振幅”(peak to peak jitter amplitude)。“jitter半振幅”(jitter-amplitude)就是你女友實際來的時間和7點之間的差值。女友來的時間有早有晚,jitter半振幅也有正有負。通過計算,你可以找出jitter半振幅的平均值,如果你能夠計算出你女友最有可能在哪個時間來,你就可以發現女友來的時間是完全無規律的(隨機jitter random jitter)還是和某些特定事情有關係(關聯jitter correlated jitter)。所謂關聯jitter就是比如你知道你的女友周四要晚來,因為她要去看她的媽媽。如果你能徹底明白這點,你就已經是一個correlated jitter的專家了。

原理理論

確定性Jitter(DJ)定義

“確定性Jitter是具有一個非高斯機率密度函式的Jitter,確定性jitter總是在幅度上跳躍的並在特定的原因下發生,四種確定性jitter被定義:占空比失真jitter、數據從屬jitter、正弦jitter和不相關(對數據)跳躍jitter,DJ的特性由它的跳躍和峰峰值決定。

DJ的形式有幾種,時鐘信號是典型的易受占空比失真(DCD)和周期Jitter(PJ)的影響的,數據信號也容易受DCD和PJ的影響,還易受符號間干擾(ISI)和數據從屬Jitter(DDJ)的影響。不管採樣尺寸如何改變,只要充足的數據點被採集以完成每個周期元素的至少一個完全的周期,那么DJ的總量將保持不變。

圖2:串擾例子

DJ來自於哪裡?

DJ是典型的由串擾、EMI、同步開關輸出(SSO)、設備功能從屬和其它有規律發生的干擾信號引起的,當一根受影響的線(一個電路板上的一根走線或一個電纜中的2根鄰近的線)被一根驅動線上產生的磁場影響時,串擾發生。(圖2)受影響的導體的感應係數的增加將使感應磁場轉換為感應電流,感應電流的累加(正極或負極)將使被影響的線的電流逐漸增加或電壓逐漸減小,電壓的逐漸減小將在被影響的線上引起jitter。

圖3總出示了一個EMI輻射圖表,一根受影響的線被來自於一個EMI源(開關電源、AC電源線、RF信號源等等)的磁場所影響,這與串擾產生的jitter非常相似,在串擾情況下,一個磁場將感應出一個感應電流,該感應電流(正極或負極)將使被影響的線上的電流增加, 因此在被影響的線上產生jitter。

圖3:EMI例子

圖4出示了一個噪聲參考平面的例子,當電源平面的噪聲引起下游邏輯門的門限電壓的參考改變時,DJ的這種形式發生。這個改變與輸入信號的迴轉率成比例,當Vt在門上被超過,輸出電晶體將導通。

當地參考平面在Vt 有一個改變時,這個電壓的改變將導致門的開關的超前或滯後,由此產生的時間誤差引起jitter。

圖4:噪聲參考平面圖表

同步開關輸出(SSO)是DJ的另一個來源,一個SSO圖表在圖5中顯示,如果幾個輸出管腳轉換到同一個狀態,將在Vcc和GND平面上感應出一個電流尖峰。

這些尖峰電流可以引起門限電壓判斷點的改變,由於模式的敏感性和由於SSO造成的jitter邊緣幅度的跳躍,這被認為是DJ。

圖5:同步開關輸出(SSO)圖表

下面的四個DJ成分被指定到數據。

符號間干擾(ISI)定義

“數據從屬確定性jitter是由信號從比特序列(符號)的不同位置開始併到達接收器門限所必需的時間差異所引起的。例如,當使用那些削弱由交替的0,1,0,1組成的比特序列的峰值幅度比由0,0,0,0,1,1,1,1組成的比特序列的峰值幅度多的媒體時,使用0,1,0,1達到接收器門限所必需的時間比來自於0,0,0,0,1,1,1,1所必需的時間少。4比特序列的運行長度產生一個更高的幅度,這將在比特值改變時花費更多的時間來克服,因此與1比特序列運行長度比較將產生一個時間差。當不同運行長度的比特序列在同一個傳輸中混合套用時,不同的比特序列(符號)將互相干擾。is expected 無論任何一種具有頻率成分的比特序列被傳輸媒體以不同的速度傳輸時,ISI將發生。

圖6:DDJ/ISI例子

數據從屬Jitter(DDJ)定義

當傳輸模式從一個時鐘模式改變到一個非時鐘模式時,Jitter被產生,包括ISI。

圖6出示了一個DDJ/ISI影響一個光纖信道K285模式的例子,在一個1,0,1,0,1,1轉換後面跟著5個0。這5個連續的0與1,0,1,0,1,1部分期間立即跳回到1的兩個0相比較轉變為一個較低的電壓。

占空比失真(DCD)定義

在一個時鐘(重複的0,1,0,1,….)比特序列中,一個“1”脈衝的平均脈衝寬度與一個“0”脈衝的平均脈衝寬度項比較的差異。DCD是DJ分布的一部分並在理想的接收器門限點被測量。

跳躍的不相關的Jitter定義

“確定性jitter由被測信號上的不同的數據所引起。

周期Jitter(PJ)定義

PJ可以量化來自於EMI源的串擾的影響。(鄰近的線、電源噪聲等等)

RMS Jitter(RMSJ)或隨機Jitter(RJ)定義

該Jitter的特性表現為一個高斯分布,隨機jitter被定義為峰峰值,該值為一比特誤差率(BER)10- e12的高斯分布的標準偏差的14倍。RMS jitter是jitter的均方根或標準偏差,對於一個高斯分布,RMS值為BER 10-e12的峰峰值的1/14。

隨機(高斯)jitter在自然界中是隨機的,它典型的表現為一個高斯分布的特點,RJ將隨著時間繼續的增加,這就是為什麼隨機jitter被提及為極大的原因。

RJ來自於哪裡?

象所有的物理現象一樣,發生在電子信號中的邊緣偏差將包括隨機行為的一些水平, 這些成分在自然界中是機率統計的並且可以被一個高斯函式最好的建模,隨機jitter是極大的,因此直接的影響長期的可靠性。

隨機jitter來自於半導體晶體結構的熱震動,由於不規則塗料密度和加工的不規則性,導體原子的熱震動和許多小的貢獻者(宇宙輻射等等),材料邊界小於理想的原子價電子映射(valence electron mapping)。

因為RMS jitter的特性為一個高斯分布,下一部分將描述高斯模型以及它如何被套用到jitter。

介紹高斯分布

要了解jitter的測量,了解高斯分布是非常重要的,因為它關係到機率問題。圖7出示了一個理想的高斯分布,描述一個高斯分布的三個基本元素為平均值、標準偏差(1s)和峰峰值。平均值是所有採樣值的平均,峰峰值是最大的測量值減去最小的測量值的結果,1s是包括所有測量的68.26%到平均值的一邊的視窗,相似的,2s 是包括所有測量的95.4%到平均值的一邊的視窗,3s是測量的99.73%,4s是測量的99.99366%等等,直到10s是測量的(100-1.973x10-21)%。標準偏差或1s用於預計來自於平均值的邊遠測量的發生,在電子學中,知道來自於理想的/指定的位置的邊緣偏差的頻率是非常重要的,例如,如果你的系統在一個1 GHz(1,000ps)的時鐘上不能容忍少於900ps的時鐘周期,你就想知道少於的一個周期的機率將是多少。短周期尾部的知識(Knowledge of the short period tail)可以精確的告訴你一個900ps周期出現的頻繁程度。

圖7:理想的高斯分布

關於這個模型,有幾個事情需要注意。首先也是最重要的,標準偏差或1s作為RMS jitter的成分使用只有在純粹的高斯分布時才是正確的,如果在你的分布中存在任何確定性成分,基於評估發生機率的完全的jitter柱狀圖的1s使用是不正確的。

其次,在純高斯數學中,所有可能的測量被假設為可能的,然而對於所有實際的目的,只有當測量的總量不超過1021時,高斯模型在電子學中才能保證結果的正確,這等效於20s(單邊)。在20s以後, 高斯模型開始終止測量的可預測性。20s的可靠性相當於一個1 GHz時鐘正常操作至少32,150.2年。第三,峰峰值由樣本尺寸決定,相同分布的大的樣本將有可能產生一個大的峰峰值測量結果,因此,峰峰值必須根據樣本數字的前後關係和測量需要的全部時間來討論。如果一個1 GHz時鐘的100個測量結果以每隔25ms測試一個周期被產生,這些樣本的統計值比同樣的1GHz時鐘的100個連續周期的測量更好,100個25ms樣本測量完需要2.5ms,而100個連續的測量結果只需100ns,25ms樣本的大的總時間視窗給出一個更好的信號完整性統計察看。

計算標準偏差(1 s)

下面是標準偏差的計算公式。

例如,如果我有8個測量結果,它們的值為2.00、2.02、2.10、2.20、1.99、1.98、1.99和2.00 ns,那么標準偏差將是

在大多數情況下,時間測量值不是完全的高斯分布的,典型的情況是一些DJ的發生導致一個非高斯的分布。

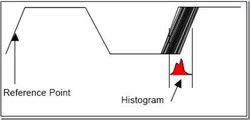

圖8出示了一個帶有DJ的並且不是完全的高斯分布的分布例子。但是,區域的尾部Ltail(紅色實線區域)和Rtail(藍色實線區域)在本質上仍然表現為高斯分布,如果並且只能如果尾部區域的等效1s可以被計算,那么該分布仍可以被假設為高斯分布。

圖8:非高斯分布

TailFitTM運算法則

專利權未定的TailFitTM運算法則使用戶能夠通過一個帶有對稱尾部區域的高斯曲線表示一個被評估的非高斯分布,不同的高斯曲線與分布的尾部區域相比對直到一個最佳的匹配被發現為止。然後,匹配曲線的1s(1sL表示左邊的)被用作那個特殊尾部的標準偏差乘積因子,這對分布的兩邊是重複的。注意,匹配的高斯分布對每個尾部不是必須相同的,圖9出示了一個右邊尾部(Rt-rmsJ)比左邊尾部(Lt -rmsJ)具有一個大的1s的例子。一旦左邊和右邊1s值被建立,總的DJ是適合分布的兩個高斯曲線的平均值的差異,根據這個DJ值以及右邊和左邊1s值,我們可以計算總的jitter時間。在圖9中,一個231.953ps的總的jitter在10-e12比特誤差率(BER)或在該時鐘的1012周期以後被計算。

圖9:TailFit™運算法則

Jitter調製

圖10齣示了jitter調製在一個同步系統上的影響,在這個圖表中有三個信號,第一個信號是一個理想的沒有jitter的時鐘,第二個信號是一個正在被調製的時鐘,第三個信號是調製函式。當調製信號為高時,它將增加被作用時鐘的周期的長度。

當調製信號為低時,它將減小被作用時鐘的周期的長度。注意,如果你測量11個周期(調製周期),你將對理想的時鐘和jitter時鐘得到相同的測量結果。這是一個周期性Jitter(PJ)的例子。

圖10:Jitter調製結果

圖11出示了一個jitter組成的分類細目,它是這篇論文的要點。

概要:

Jitter由許多元素組成,因為隨機jitter是極大的,因此你必須量化你的jitter指標,通過使用TailFitTM運算法則將全部的jitter分類細化為它的基本組成部分:確定性jitter和隨機性jitter,我們可以及時的計畫出並在一個想要的BER或時間得到一個全部的jitter數,從而對jitter進行量化。

圖11:jitter組成的分類細目圖表

分類

抖動有兩種主要類型:確定性抖動和隨機性抖動。

確定性抖動是由可識別的干擾信號造成的,這種抖動通常幅度有限,具備特定的(而非隨機的)產生原因,而且不能進行統計分析。

隨機抖動是指由較難預測的因素導致的時序變化。例如,能夠影響半導體晶體材料遷移率的溫度因素,就可能造成載子流的隨機變化。另外,半導體加工工藝的變化,例如摻雜密度不均,也可能造成抖動。

描述方法

可以通過許多基本測量指標確定抖動的特點,基本的抖動參數包括:

1)周期抖動(period jitter)

測量實時波形中每個時鐘和數據的周期的寬度。這是最早最直接的一種測量抖動的方式。這一指標說明了時鐘信號每個周期的變化。

2)周期間抖動(cycle-cycle jitter)

測量任意兩個相鄰時鐘或數據的周期寬度的變動有多大,通過對周期抖動套用一階差分運算,可以得到周期間抖動。這個指標在分析瑣相環性質的時候具有明顯的意義。

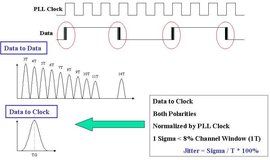

3)時間間隔誤差(timer interval error,TIE)

測量時鐘或數據的每個活動邊沿與其理想位置有多大偏差,它使用參考時鐘或時鐘恢復提供理想的邊沿。TIE在通信系統中特別重要,因為他說明了周期抖動在各個時期的累計效應。

頻域表示

--相位噪聲

相位噪聲是對信號時序變化的另一種測量方式,其時間抖動(jitter)在頻率域中的顯示。圖2用一個振盪器信號來解釋相位噪聲。

如果沒有相位噪聲,那么振盪器的整個功率都應集中在頻率f=fo處。但相位噪聲的出現將振盪器的一部分功率擴展到相鄰的頻率中去,產生了邊帶(sideband)。從圖2中可以看出,在離中心頻率一定合理距離的偏移頻率處,邊帶功率滾降到1/fm,fm是該頻率偏離中心頻率的差值。

相位噪聲通常定義為在某一給定偏移頻率處的dBc/Hz值,其中,dBc是以dB為單位的該頻率處功率與總功率的比值。一個振盪器在某一偏移頻率處的相位噪聲定義為在該頻率處1Hz頻寬內的信號功率與信號的總功率比值。