處理器

作為獨立處理器,Cortex-A7 可以使 2013-2014 年期間低於 100 美元價格點的入門級智慧型手機與 2010 年 500 美元的高端智慧型手機相媲美。這些入門級智慧型手機在發展中世界將重新定義連線和 Internet 使用

規格

| Cortex-A7 MPCore | |

| 架構 | ARMv7-A Cortex |

| 多核 | 單處理器群集中的 1-4X SMP通過 AMBA® 4 技術實現多個一致的 SMP 處理器群集 |

| ISA 支持 | ARMThumb-2TrustZone® 安全技術NEON™ 高級 SIMDDSP & SIMD 擴展VFPv4 浮點Jazelle® RCT硬體虛擬化支持大物理地址擴展 (LPAE) |

| 記憶體管理 | ARMv7 記憶體管理單元 |

| 調試和追蹤 | CoreSight™ SoC-400 |

| Cortex-A7 MPCore 主要功能 | |

| Thumb-2 技術 | 可為傳統 ARM 代碼提供最高性能,對於存儲指令占用的記憶體,最多可節省 30% 的空間。 |

| TrustZone 技術 | 確保全全套用的可靠實現,適合從數字著作權管理到電子支付等套用。 |

| NEON | NEON 技術可加速多媒體和信號處理算法(如視頻編碼/解碼、2D/3D 圖形、遊戲、音頻和語音處理、圖像處理技術、電話和聲音合成)。 |

| DSP 和 SIMD 擴展 | 增加高性能套用中 ARM 解決方案的 DSP 處理能力,同時通過攜帶型、電池電源設備提供所需的低功耗。DSP 擴展經過最佳化,適用於範圍廣泛的軟體套用,包括伺服馬達控制、VoIP 和視頻音頻編解碼器。 |

| 浮點 | 對半精度、單精度和雙精度浮點運算中的浮點操作提供硬體支持。Cortex-A7 處理器的浮點功能增強了下一代消費類產品(如 Internet 設備、機頂盒和家用網關)中使用的浮點運算的性能。 |

| Jazelle RCT | 最多可使即時生產 (JIT) 和提前編譯的位元組碼語言的代碼大小縮小 3 倍,以便提高傳統虛擬機的速度。 |

| 硬體虛擬化 | 針對數據管理和仲裁的高效硬體支持,通過此方式,多個軟體環境及其應用程式將能夠同時訪問系統功能。這樣,就實現了可靠、具有相互隔離的虛擬環境的設備。 |

| 大物理地址擴展 (LPAE) | 大物理地址擴展 (LPAE) 的引入允許處理器可訪問最大 1TB 記憶體。 |

| 最佳化的 1 級高速快取 | 性能和功率最佳化的 L1 高速快取結合了最低訪問延遲技術,可以在最大程度上提高性能和降低功耗。高速快取中可配置大小的 8kB~64KB 用於指令和數據。還為實現高速快取一致性提供了增強處理器間通信的選項或支持富 SMP 功能作業系統的選項,以便簡化多核軟體開發。 |

| 集成、可配置大小的 2 級高速快取控制器 | 在高頻率設計或需要降低與晶片外記憶體訪問關聯的能耗的設計中,最多可對 1 MB 高速快取記憶體提供低延遲、高頻寬訪問。L2 高速快取在 Cortex-A7 上是可選的。 |

| AMBA® 4 高速快取一致性互連 (CCI) | CCI 提供符合 AMBA 4 AXI™ 一致性擴展 (ACE) 的連線埠,以在多個 Cortex-A7 MPCore 處理器之間實現完全一致,可以更好地利用高速快取並簡化軟體開發。此功能對於高頻寬套用是必需的,包括需要一致的單核和多核處理器的群集的遊戲、伺服器和網路。CCI 與 ARM CoreLink™ 網路互連和記憶體控制器 IP 相結合,提高了系統性能和能效。 |

| Cortex-A7 NEON 媒體處理引擎 (MPE) | Cortex-A7 MPE 提供了一個引擎,該引擎可同時提供 Cortex-A7 浮點單元的性能和功能以及 NEON 高級 SIMD 指令集實現,以便進一步提高媒體和信號處理功能的速度。MPE 擴展了 Cortex-A7 處理器的浮點單元 (FPU) 以提供一個 quad-MAC 以及附加的 64 位和 128 位暫存器集,在 8 位、16 位和 32 位整型以及 32 位浮點數據量的基礎上支持一組豐富的 SIMD 操作。 |

| Cortex-A7 浮點單元 (FPU) | FPU 提供了與 ARM VFPv4 體系結構兼容的高性能的單雙精度浮點指令,該體系結構是與上一代 ARM 浮點協處理器兼容的軟體。 |

技術支持

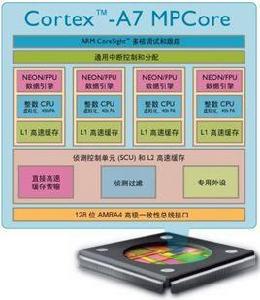

Cortex-A7 MPCore 處理器融合了各種各樣的 ARM 技術並由這些技術提供支持,包括系統 IP、物理 IP 和開發工具。此技術由來自 ARM Connected Community™ 的各種不同 SoC 和軟體設計解決方案、工具和服務提供補充,為 ARM 合作夥伴提供了一個涵蓋全功能開發、驗證和生產的通道,增加了設備的吸引力同時顯著縮短了上市時間。

系統 IP

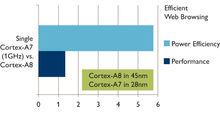

Cortex-A7與A8處理器在網頁瀏覽中的對比

Cortex-A7與A8處理器在網頁瀏覽中的對比ARM CoreLink™ 互連和記憶體控制器 IP 解決了在多個 Cortex-A7 MPCore 處理器、高性能媒體處理器和動態記憶體之間高效移動和存儲數據的重大難題,最佳化了 SoC 的系統性能和功耗。使用 CoreLink 系統 IP,SoC 設計人員可以最大限度地利用記憶體頻寬並縮短靜態和動態延遲。ARM CoreSight™ 技術不僅提供了有關 Cortex-A7 MPCore 處理器的所有核心的完整片上調試和相關的實時跟蹤可見性,還降低了風險並加快了高質量多處理軟體的開發速度。最佳系統頻寬和延遲由全新的 AMBA® 4 高速快取互連(CCI) 提供。CCI 提供符合 AMBA 4 AXI™ 一致性擴展 (ACE) 的連線埠,以在多個 Cortex-A7 MPCore 處理器之間實現完全一致,可以更好地利用高速快取並簡化軟體開發。此功能對於高頻寬套用是必需的,包括需要一致的單核和多核處理器的群集的遊戲、伺服器和網路。CCI 與 ARM CoreLink 網路互連和記憶體控制器 IP 相結合,提高了系統性能和能效。

物理 IP

ARM 物理 IP平台可提供工藝上得到最佳化的 IP,從而能夠在採用 40 納米及以下工藝時獲得同類最佳的 Cortex-A7 處理器實現。Cortex-A15 處理器由一組高性能處理器最佳化包 (POP) 提供支持,這些最佳化包中包含適用於 28 納米技術的高級 ARM 物理 IP,支持快速開發領先的物理實現。ARM 還在很早就著手準備,確保遵循旨在實現 20nm 最佳化的路線圖。最佳化包支持 ARM 旨在提供專用型物理 IP 的戰略,以支持合作夥伴獲得最佳化的 ARM 核心實現。ARM 獨家擁有同時設計最佳化包和 Cortex-A7 MPCore 處理器體系結構的功能,支持組合使用處理器和物理 IP 以在移動功率包絡中提供工作站級性能,同時加快上市速度。

工具支持

所有 ARM 處理器在 ARM Development Suite 5 (DS-5™) 工具套件和範圍廣泛的第三方工具、作業系統和 EDA 流中都是完全受支持的。ARM DS-5 軟體開發工具獨一無二,能夠提供的解決方案充分利用完整 ARM 技術組合的優勢。ARM Development Studio 5 (DS-5™) 提供了一整套軟體工具,用於創建、調試和最佳化基於 Cortex-A15 MPCore 處理器的系統。它納入了 DS-5 調試器,該調試器具有強大且直觀的圖形環境,支持快速調試裸機、Linux 和 Android 本機應用程式。此外,其中包含的全新 ARM Streamline™ 性能分析器簡化了軟體中的熱點識別和核心之間的負載平衡。ARM 編譯器支持在晶片可用之前進行早期軟體開發,此編譯器已包括針對 Cortex-A15 MPCore 處理器的特定最佳化,ARM Versatile™ 參考虛擬平台基於 ARM 快速模型技術構建。此虛擬平台可供 6 個月免費評估。

相關產品

截止到2014年已上市的Cortex-A7晶片有聯發科的MT6589(含有MT6589M、MT6589T和普通版MT6589三種規格)和全志A31 。都是四核芯產品。

其中MT6589系列被廣泛用於2013年的千元安卓智慧型手機,如紅米,華為G700/610,中興U956等。