概述

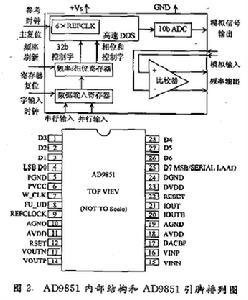

AD9851

AD9851各引腳介紹

D0~D7: 8位數據輸入口,可給內部暫存器裝入40位控制數據。

PGND:6倍參考時鐘倍頻器的地。

PVCC:6倍參考時鐘倍頻器電源。

W—CLK:字裝入信號,上升沿有效。

FQ—UD:頻率更新控制信號,時鐘上升沿確認輸入數據有效。

REFCLOCK:外部參考時鐘輸入。

AGND:模擬地。

AVDD:模擬電源(+5V)。

DGND:數字地。

DVDD:數字電源(+5V)。

Rset:通過串聯一個電阻到地,設定DAC輸出滿額時的電流。

VOUTN:內部比較器負向輸出端。

VOUTP:內部比較器正向輸出端。

VINN:內部比較器負向輸入端。

VINP:內部比較器正向輸入端。

DACBP:DAC旁路連線端。

IOUTB:”互補“DAC輸出。

IOUT:內部DAC輸出端。

RESET:復位端。

原理分析

AD9851採用直接數字合成(DDS)技術,以數字控制振盪器(DCO)的形式產生頻率/相位可變的正弦波,經過內部10位的高速數/ 模轉換輸出模擬信號。片內高速比較器可以將模擬正弦波信號轉變為穩定的TTL/CMOS兼容的方波輸出。

AD9851高速DDS核心可接收32位的頻率控制字輸入,在180MHz的系統時鐘下可輸出的頻率解析度為180MHz/(2的32次方)。AD9851內部提供一個6倍頻的REFCLK倍頻器,可以通過外接一個較低頻率的基準時鐘產生180MHz的內部基準時鐘,具有較好的無雜散動態範圍和相位噪聲特性。晶片內部提供了5位可程式相位調製精度,可使得輸出波形的相位偏移小於11.25度;AD9851內部華提供了一個高速比較器,內部D/A轉換器輸出的正弦波可以通過它轉換為方波輸出。

AD9851頻率控制字、相位調節字以及可以採用並行或串列方式異步載入到晶片內部。並行載入模式有連續5個8位位元組構成,其中第一個8位位元組包括5位相位調節字、1位6*REFCLK倍頻器控制、1位電源休眠使能和一位載入模式;其餘4個位元組表示32位的頻率控制字。串列載入模式由40位的數據流構成。

DDS電路可以看成是一個由系統時鐘和N位頻率控制字決定的數字分頻器,相位累加器相當於模值可變的計數器。由頻率控制字決定該計數器的模值,在下一個時鐘脈衝開始相位累加器以新的相位增量進行累加。設定的相位增量越大,累加器循環一周就越快,從而輸出的頻率就越高。