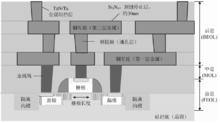

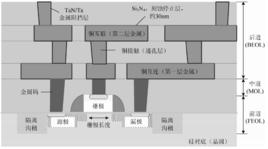

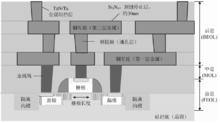

圖1是一個邏輯器件的剖面示意圖。新的集成技術在晶圓襯底上也添加了很多新型功能材料,例如:前道(FEOL)柵極的高介電常數材料,它能有效地增大柵極的電容並減少漏電流。前道(FEOL)中的關鍵光刻層是 FIN 和柵極(gate)。後道(BEOL)的關鍵光刻層是 V0/M1/V1/M2,其中V0/V1是通孔層,M1/M2是金屬層 。

前道工藝

前道工藝圖1 一個邏輯器件的剖面示意圖

積體電路是依靠所謂的平面工藝一層一層製備起來的。對於邏輯器件,簡單地說,首先是在 Si襯底上劃分製備電晶體的區域(active area),然後是離子注入實現N型和P型區域,其次是做柵極,隨後又是離子注入,完成每一個電晶體的源極(source)和漏極(drain)。這部分工藝流程是為了在 Si 襯底上實現N型和P型場效應電晶體,又被稱為前道(front end of line,FEOL)工藝。

圖1是一個邏輯器件的剖面示意圖。新的集成技術在晶圓襯底上也添加了很多新型功能材料,例如:前道(FEOL)柵極的高介電常數材料,它能有效地增大柵極的電容並減少漏電流。前道(FEOL)中的關鍵光刻層是 FIN 和柵極(gate)。後道(BEOL)的關鍵光刻層是 V0/M1/V1/M2,其中V0/V1是通孔層,M1/M2是金屬層 。

前道工藝

前道工藝圖1 一個邏輯器件的剖面示意圖

在產品加工過程中,需要一道以上的工序才能夠完成,那么,除第一道工序外,對於第二、第三....直至最後一道工序,都可以被叫做前一道工序的“後道工序”。同樣...

非織造後道工藝裝備技術創新的若干探討 裝潢印刷後道工藝裝備的發展趨勢磷化工藝過程是一種化學與電化學反應形成磷酸鹽化學轉化膜的過程,所形成的磷酸鹽轉化膜稱之為磷化膜。磷化的目的主要是:給基體金屬提供保護,在一定程度上防止金...

原理 分類 預處理 工藝 塗裝工藝不同的焊接方法有不同的焊接工藝。焊接工藝主要根據被焊工件的材質、牌號、化學成分,焊件結構類型,焊接性能要求來確定。首先要確定焊接方法,如手弧焊、埋弧焊、...

工藝要點 焊接方法 注意事項 焊接器材 焊接溫度控制前峰雪蓮是江蘇省80年代新創新的名茶之一。1985年在農牧漁業部、中國前峰雪蓮學會聯合召開的中國名茶展評會上,被評為部優質茶。1989年中國名茶評比會上...

生態環境 品質特點 藥理功效 製作工藝 沖泡技巧熱流道(anole hot runner)是在注塑模具中使用的,將融化的塑膠粒子注入到模具的型腔中的加熱組件系統。

原理 特點 結構 組成 漏料處理。該工藝主要包括生絲及織物的精煉、染色、印花和整理四道加工工序。 第一道為...織物進行最後的整理工作。整理工藝主要解決前幾道工序遺留的潮濕、皺摺、門幅...發展歷程 染整工藝 絢麗多彩的絲綢是精緻的染整工藝的結晶。印花工序...

簡介 織物染整工藝的名詞解釋 染整技術特點 相關書籍 適用對象雕漆工藝,是把天然漆料在胎上塗抹出一定厚度,再用刀在堆起的平面漆胎上雕刻花紋的技法。由於色彩的不同,亦有"剔紅"、"剔黑"、"剔彩"及"剔犀"等不同的名目。

簡介 溯源與發展 工藝及特點 原料與輔料 工具設備明前茶是按節氣對不同階段春茶的稱呼。明前茶由於芽葉細嫩,香氣物質和滋味物質含量豐富,因此品質非常好,被認為是茶葉中的上品。

簡介 認識誤區 來歷 區分 購買注意事項香道是歷史悠久的漢族傳統藝術,就是通過眼觀、手觸、鼻嗅等品香形式對名貴香料進行全身心的鑑賞和感悟,並且在略帶表演性的程式中,堅守令人愉悅和規矩的秩序,使...

作用 香道朔源 四大香藥 香木 太月派香學