基本概念

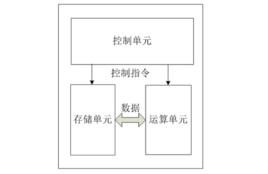

中央處理器(CPU,Central Processing Unit)是一塊超大規模的積體電路,是一台計算機的運算核心(Core)和控制核心( Control Unit)。它的功能主要是解釋計算機指令以及處理計算機軟體中的數據。CPU從邏輯上可以劃分成3個模組,分別是控制單元、運算單元和存儲單元,這三部分由CPU內部匯流排連線起來。

中央處理器存儲器又叫CPU存儲器,CPU存儲器是微處理器中存放數據和各種程式的裝置。CPU存儲器是微處理器的一個重要的組成部分,由存儲單元集合體,地址暫存器,解碼驅動電路,讀出放大器以及時序控制電路等幾部分組成。

CPU結構

CPU的根本任務就是執行指令,對計算機來說最終都是一串由“0”和“1”組成的序列。CPU從邏輯上可以劃分成3個模組,分別是控制單元、運算單元和存儲單元,這三部分由CPU內部匯流排連線起來。如下所示:

中央處理器存儲器

中央處理器存儲器CPU存儲器包括CPU片內快取和暫存器組,是CPU中暫時存放數據的地方,裡面保存著那些等待處理的數據,或已經處理過的數據,CPU訪問暫存器所用的時間要比訪問記憶體的時間短。採用暫存器,可以減少CPU訪問記憶體的次數,從而提高了CPU的工作速度。但因為受到晶片面積和集成度所限,暫存器組的容量不可能很大。暫存器組可分為專用暫存器和通用暫存器。專用暫存器的作用是固定的,分別暫存相應的數據。而通用暫存器用途廣泛並可由程式設計師規定其用途,通用暫存器的數目因微處理器而異。

暫存器類型

CPU 的通用暫存器是數據存儲體系的最內層。暫存器操作避免了記憶體地址計算, 其訪問時間遠小於Cache

和主存。

數據暫存器

數據暫存器主要用來保存運算元和運算結果等信息,從而節省讀取運算元所需占用匯流排和訪問存儲器的時間。

32位CPU有4個32位的通用暫存器EAX、EBX、ECX和EDX。對低16位數據的存取,不會影響高16位的數據。這些低16位暫存器分別命名為:AX、BX、CX和DX,它和先前的CPU中的暫存器相一致。

4個16位暫存器又可分割成8個獨立的8位暫存器(AX:AH-AL、BX:BH-BL、CX:CH-CL、DX:DH-DL),每個暫存器都有自己的名稱,可獨立存取。程式設計師可利用數據暫存器的這種“可分可合”的特性,靈活地處理字/位元組的信息。

暫存器AX和AL通常稱為累加器(Accumulator),用累加器進行的操作可能需要更少時間。累加器可用於乘、除、輸入/輸出等操作,它們的使用頻率很高;

暫存器BX稱為基地址暫存器(Base Register)。它可作為存儲器指針來使用;

暫存器CX稱為計數暫存器(Count Register)。在循環和字元串操作時,要用它來控制循環次數;在位操作中,當移多位時,要用CL來指明移位的位數;

暫存器DX稱為數據暫存器(Data Register)。在進行乘、除運算時,它可作為默認的運算元參與運算,也可用於存放I/O的連線埠地址。

在16位CPU中,AX、BX、CX和DX不能作為基址和變址暫存器來存放存儲單元的地址,但在32位CPU中,其32位暫存器EAX、EBX、ECX和EDX不僅可傳送數據、暫存數據保存算術邏輯運算結果,而且也可作為指針暫存器,所以,這些32位暫存器更具有通用性。詳細內容請見第3.8節——32位地址的定址方式。

變址暫存器

32位CPU有2個32位通用暫存器ESI和EDI。其低16位對應先前CPU中的SI和DI,對低16位數據的存取,不影響高16位的數據。

暫存器ESI、EDI、SI和DI稱為變址暫存器(Index Register),它們主要用於存放存儲單元在段內的偏移量,用它們可實現多種存儲器運算元的定址方式(在第3章有詳細介紹),為以不同的地址形式訪問存儲單元提供方便。

變址暫存器不可分割成8位暫存器。作為通用暫存器,也可存儲算術邏輯運算的運算元和運算結果。

它們可作一般的存儲器指針使用。在字元串操作指令的執行過程中,對它們有特定的要求,而且還具有特殊的功能。

指針暫存器

32位CPU有2個32位通用暫存器EBP和ESP。其低16位對應先前CPU中的SBP和SP,對低16位數據的存取,不影響高16位的數據。

指針暫存器不可分割成8位暫存器。作為通用暫存器,也可存儲算術邏輯運算的運算元和運算結果。

它們主要用於訪問堆疊內的存儲單元,並且規定:

BP為基指針(Base Pointer)暫存器,用它可直接存取堆疊中的數據;

SP為堆疊指針(Stack Pointer)暫存器,用它只可訪問棧頂。

段暫存器

段暫存器是根據記憶體分段的管理模式而設定的。記憶體單元的物理地址由段暫存器的值和一個偏移量組合而成的,這樣可用兩個較少位數的值組合成一個可訪問較大物理空間的記憶體地址。

CPU內部的段暫存器:

CS——代碼段暫存器(Code Segment Register),其值為代碼段的段值;

DS——數據段暫存器(Data Segment Register),其值為數據段的段值;

ES——附加段暫存器(Extra Segment Register),其值為附加數據段的段值;

SS——堆疊段暫存器(Stack Segment Register),其值為堆疊段的段值;

FS——附加段暫存器(Extra Segment Register),其值為附加數據段的段值;

GS——附加段暫存器(Extra Segment Register),其值為附加數據段的段值。

在16位CPU系統中,它只有4個段暫存器,所以,程式在任何時刻至多有4個正在使用的段可直接訪問;在32位微機系統中,它有6個段暫存器,所以,在此環境下開發的程式最多可同時訪問6個段。

32位CPU有兩個不同的工作方式:實方式和保護方式。在每種方式下,段暫存器的作用是不同的。有關規定簡單描述如下:

實方式: 前4個段暫存器CS、DS、ES和SS與先前CPU中的所對應的段暫存器的含義完全一致,記憶體單元的邏輯地址仍為“段值:偏移量”的形式。為訪問某記憶體段內的數據,必須使用該段暫存器和存儲單元的偏移量。

保護方式: 在此方式下,情況要複雜得多,裝入段暫存器的不再是段值,而是稱為“選擇子”(Selector)的某個值。段暫存器的具體作用在此不作進一步介紹了,有興趣的讀者可參閱其它科技資料。

指令暫存器

32位CPU把指令指針擴展到32位,並記作EIP,EIP的低16位與先前CPU中的IP作用相同。

指令指針EIP、IP(Instruction Pointer)是存放下次將要執行的指令在代碼段的偏移量。用來提供指令在存儲器中的地址。在具有預取指令功能的系統中,下次要執行的指令通常已被預取到指令佇列中,除非發生轉移情況。所以,在理解它們的功能時,不考慮存在指令佇列的情況。

在實方式下,由於每個段的最大範圍為64K,所以,EIP中的高16位肯定都為0,此時,相當於只用其低16位的IP來反映程式中指令的執行次序 。