簡介

89C52是INTEL公司MCS-51系列單片機中基本的產品,它採用ATMEL公司可靠的CMOS工藝技術製造的高性能8位單片機,屬於標準的MCS-51的HCMOS產品。它結合了CMOS的高速和高密度技術及CMOS的低功耗特徵,它基於標準的MCS-51單片機體系結構和指令系統,屬於89C51增強型單片機版本,集成了時鐘輸出和向上或向下計數器等更多的功能,適合於類似馬達控制等套用場合。89C52內置8位中央處理單元、512位元組內部數據存儲器RAM、8k片內程式存儲器(ROM)32個雙向輸入/輸出(I/O)口、3個16位定時/計數器和5個兩級中斷結構,一個全雙工串列通信口,片內時鐘振盪電路。此外,89C52還可工作於低功耗模式,可通過兩種軟體選擇空閒和掉電模式。在空閒模式下凍結CPU而RAM定時器、串列口和中斷系統維持其功能。掉電模式下,保存RAM數據,時鐘振盪停止,同時停止晶片內其它功能。89C52有PDIP(40pin)和PLCC(44pin)兩種封裝形式。

功能特性

| · 標準MCS-51核心和指令系統 | · 片內8kROM(可擴充64kB外部存儲器) |

| · 32個雙向I/O口 | · 256x8bit內部RAM(可擴充64kB外部存儲器) |

| · 3個16位可程式定時/計數器 | · 時鐘頻率3.5-12/24/33MHz |

| · 向上或向下定時計數器 | · 改進型快速編程脈衝算法 |

| · 6箇中斷源 | · 5.0V工作電壓 |

| · 全雙工串列通信口 | · 布爾處理器 |

| —幀錯誤偵測 | · 4層優先權中斷結構 |

| —自動地址識別 | · 兼容TTL和CMOS邏輯電平 |

| · 空閒和掉電節省模式 | · PDIP(40)和PLCC(44)封裝形式 |

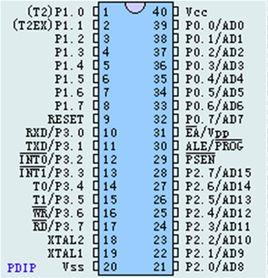

管腳說明

VCC:供電電壓。 GND:接地。

P0口:P0口為一個8位漏級開路雙向I/O口,每腳可吸收8個TTL門電流。當P0口的管腳第一次寫“1”時,被定義為高阻輸入。P0能夠用於外部程式數據存儲器,它可以被定義為數據/地址的第八位。在FLASH編程時,P0 口作為原碼輸入口,當FLASH進行校驗時,P0輸出原碼,此時P0外部必須被拉高。

P1口:P1口是一個內部提供上拉電阻的8位雙向I/O口,P1口緩衝器能接收輸出4個TTL門電流。P1口管腳寫入“1”後,被內部上拉為高,可用作輸入,P1口被外部下拉為低電平時,將輸出電流,這是由於內部上拉的緣故。在FLASH編程和校驗時,P1口作為低八位地址接收。

P2口:P2口為一個內部上拉電阻的8位雙向I/O口,P2口緩衝器可接收,輸出4個TTL門電流,當P2口被寫“1”時,其管腳被內部上拉電阻拉高,且作為輸入。並因此作為輸入時,P2口的管腳被外部拉低,將輸出電流。這是由於內部上拉的緣故。P2口當用於外部程式存儲器或16位地址外部數據存儲器進行存取時,P2口輸出地址的高八位。在給出地址“1”時,它利用內部上拉優勢,當對外部八位地址數據存儲器進行讀寫時,P2口輸出其特殊功能暫存器的內容。P2口在FLASH編程和校驗時接收高八位地址信號和控制信號。

P3口:P3口管腳是8個帶內部上拉電阻的雙向I/O口,可接收輸出4個TTL門電流。當P3口寫入“1”後,它們被內部上拉為高電平,並用作輸入。作為輸入,由於外部下拉為低電平,P3口將輸出電流(ILL)這是由於上拉的緣故。P3口作為AT89C51的一些特殊功能口,管腳 備選功能

P3.0 RXD(串列輸入口)

P3.1 TXD(串列輸出口)

P3.2 /INT0(外部中斷0)

P3.3 /INT1(外部中斷1)

P3.4 T0(計時器0外部輸入)

P3.5 T1(計時器1外部輸入)

P3.6 /WR(外部數據存儲器寫選通)

P3.7 /RD(外部數據存儲器讀選通)

RST:復位輸入。當振盪器復位器件時,要保持RST腳兩個機器周期的高電平時間。

ALE/PROG:當訪問外部存儲器時,地址鎖存允許的輸出電平用於鎖存地址的底位位元組。

在FLASH編程期間,此引腳用於輸入編程脈衝。在平時,ALE端以不變的頻率周期輸出正脈衝信號,此頻率為振盪器頻率的1/6。因此它可用作對外部輸出的脈衝或用於定時目的。然而要注意的是:每當用作外部數據存儲器時,將跳過一個ALE脈衝。如想禁止ALE的輸出可在SFR8EH地址上置0。此時, ALE只有在執行MOVX,MOVC指令是ALE才起用。另外,該引腳被略微拉高。如果微處理器在外部執行狀態ALE禁止,置位無效。

/PSEN:外部程式存儲器的選通信號。在由外部程式存儲器取指期間,每個機器周期兩/PSEN有效。但在訪問外部數據存儲器時,這兩次有效的/PSEN信號將不出現。/EA / VPP:當/EA保持低電平時,則在此期間外部程式存儲器(0000H-FFFFH),不管是否有內部程式存儲器。注意加密方式1時,/EA將內部鎖定為RESET;當/EA端保持高電平時,此間內部程式存儲器。在FLASH編程期間,此引腳也用於施加12V編程電源(VPP)。

XTAL1:反向振盪放大器的輸入及內部時鐘工作電路的輸入。

XTAL2:來自反向振盪器的輸出。

振盪器

外接石英晶體或者陶瓷諧振器以及電容C1、C2接在放大器的反饋迴路(AT89C52內部有一個用於構成內部振盪器的高增益反相放大電路,XTAL1、XTAL2分別是該放大器的輸入和輸出端)中構成並聯振盪電路。

為了使裝置能夠被外部時鐘信號激活,XATL1應該有效,而XTAL2應該被懸空。由於輸入到內部的時鐘信號電路通過了一個二分頻的信號,外部信號的工作周期比沒有別的要求,但是最大值和最小值的大小可以在數據表上觀察出來。

當正常工作時,外部振盪器可以計算出XTAL1上的電容,最大可達到100pF。這是由於振盪器電容和反饋電容之間的相互作用。當外部信號是標準高電平或者低電平時,電容不會超過20pF.

空置模式

用戶的軟體都可以調用空置模式。當單片機處於這種模式,耗能就會自然降低。特殊功能端和板子上的隨機存儲器在空置狀態保持各自的電平。但是處理器阻止裝置執行指令。空置模式會被激活如果連線埠處於復位狀態或者中斷系統有效。

結構特點

n 互補高性能金屬氧化物半導體結構可擦可

編程唯讀存儲器/唯讀存儲器/中央處理器

n 12/24/33MHz操作

n 三個16位的定時器/計數器

n 可程式的時鐘輸出

n Up/Down定時器/計數器

n 三級程式鎖定系統

n 8K/16K/32K片內程式存儲器

n 256位元組片內RAM

n 改進的快速脈衝編程算法

n 布爾處理器

n 32根可程式的輸入/輸出線

n 六個中斷源

n 可程式的串列通道帶有:——幀錯誤檢測

——自動地址識別

n TTL和CMOS兼容邏輯電平

n 64K片外程式存儲空間

n 64K片外數據存儲空間

n MCS51單片機可兼容指令集

n 閒置節能和掉電模式

n ONCE(On-Circuit仿真)模式

n 四級中斷優先權

n 擴展溫度範圍(﹣40℃到﹢85℃)